模拟电路迁移和优化

2023-07-19 12:11:17 EETOP编译来源:EETOP编译自semiwiki

MunEDA 用户组会议 (MUGM) 自 2006 年以来一直是一年一度的活动,今年有来自众多客户的约 80 名参与者参加,分享他们的经验并学习如何获得最佳的 EDA 工具结果。我已经能够查看演示文稿和存档视频,接下来与大家分享特定工具类别中一些有趣的成功案例。

ST的工程师做了两场演讲,介绍了他们如何借助设计自动化软件进行模拟电路移植和优化。ST的 Caroline Vaganay 在其 PDK 和设计流程小组工作,她将MunEDA 的用于模拟电路迁移的WiCkeD工具与其他供应商的三种内部设计进行了比较。

他们比较用于模拟电路迁移的 EDA 工具的标准是:

支持

他们的基准测试中使用了三个电路:

带隙

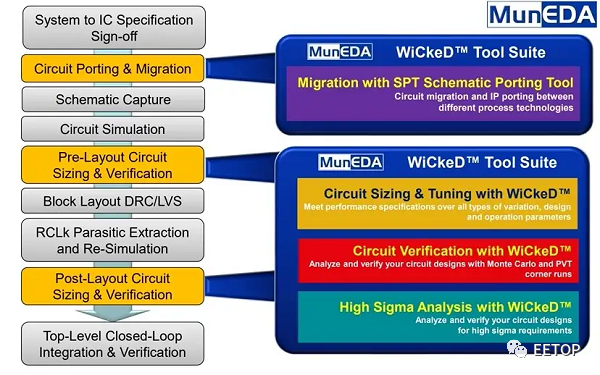

WiCkeD工具的总体设计流程如下所示:

对于设计为 0.25um 的 OPAMP 电路,他们希望通过改进所有 PVT corners的 Vio 和 Icc 来寻找更好的权衡选择,实现 PGB > 20 MHz。优化结果表明,在标称和最坏情况拐角处,所有性能值均在规格范围内,并且运行时间仅需 4 小时 5 分钟即可完成 7,455 次模拟。在最坏的情况下,性能稳健性得到改善,总良率从 14% 提高到 71%。

他们要优化的第二个电路是使用 40nm 技术的电压参考缓冲器,其目标是改善 PVT corners上的电流重新复制,以最大限度地减少任何工艺变化的影响。WiCkeD 被指示更改设计参数以减少局部变化,从而改善性能指标的标准偏差:

DELTA_PC_X8, upper, 45.7%

Caroline 的最终基准电路是 0.18um 带隙基准,其目标是优化电阻网络,以在整个温度范围内获得最小补偿曲率,同时显示稳定性并达到 PSRR、功耗和带宽目标。

WiCkeD 优化器仅通过 8,107 次模拟就能满足所有性能目标和 DC 条件,模拟时间为 9 小时 40 分钟。借助 MunEDA 工具,他们在速度和准确性上击败了其他工具,找到了其他工具无法找到的解决方案。

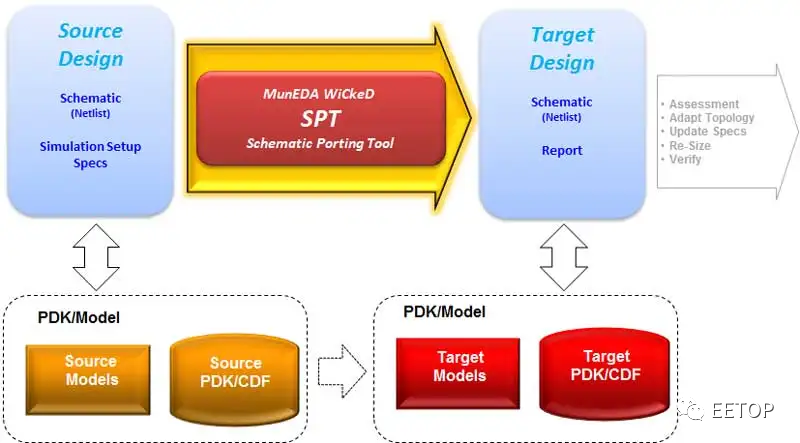

ST 的Maxime Blattes分享了他对SPT的评估,他们移植原理图的步骤是:

运行更新参数过程

他们之前使用 Cadence Virtuoso 的流程需要定制,这对于非 CAD 工程师来说很困难,并且需要技能开发人员。移植工具的承诺是节省时间和人才。SPT 是一个基于 GUI 的工具,使工程师能够更轻松、快速地完成符号映射、属性映射和自动提取原理图等任务。之前移植的最长部分是解决线路更新问题,现在通过 SPT 实现自动化。

非CAD工程师的设计师可以自行使用SPT,快速创建任何需要的模板,并在短时间内学习该工具。他们使用 SPT 只花了 30 分钟,而使用 SKILL 编码则需要大约 2 天的时间。

MunEDA 的 Matthias Sylvester 的第三次演示是 SPT 演示,其中他将 3 引脚到 3 引脚 MOS 设计的示例原理图从 180nm 移植到 90nm,然后是 3 引脚到 4 引脚 MOS。他关于原理图移植的 SPT 的主要观点是:

SPT 比其他工具更强大、更方便

模拟电路迁移和优化可以是手动过程,也可以是自动过程,ST MicroElectronics 等公司已使用 MunEDA 的 WiCkeD 工具来实现过程自动化,产生的结果满足面积、良率、性能和鲁棒性等规格。是的,模拟设计仍然一半是艺术,一半是工程,但是使用 EDA 自动化工具可以让您的工程师在比手动方法更短的时间内获得更好的结果。原理图移植工具 - SPT 是在节点和晶圆厂之间迁移任何原理图的快速方法。