带时钟接收器的 DDR5 设计方法

2023-06-21 12:12:29 EETOP编译

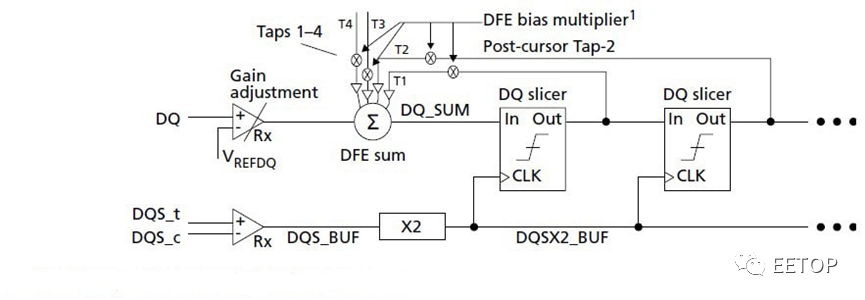

DDR5 规范中的典型 4-tap DFE

对于 DDR5,时钟是差分选通信号(DQS_t、DQS_c),并且它沿着单端数据信号 (DQ) 转发到 Rx。DQS 信号被缓冲,然后扇出到最多 8 个 DQ 锁存器的时钟输入,从而导致时钟树延迟。

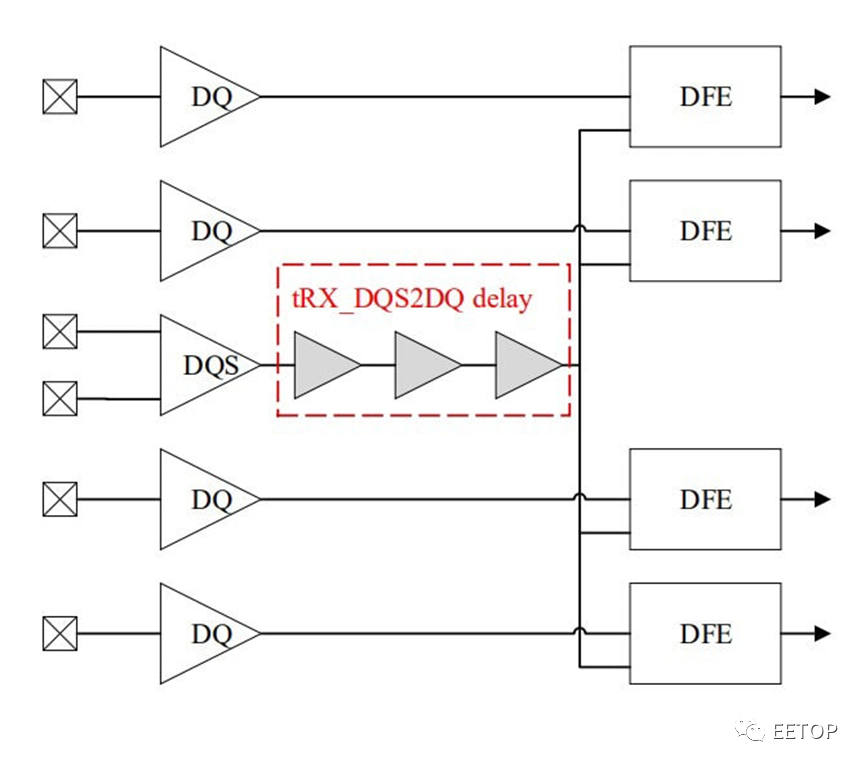

DQS 时钟树延迟

最大眼图高度为 95mV,最大眼图宽度为 0.25 单位间隔 (UI),或仅为 78.125ps。使用统计方法测量 1e-16 的 BER 是最实用的。

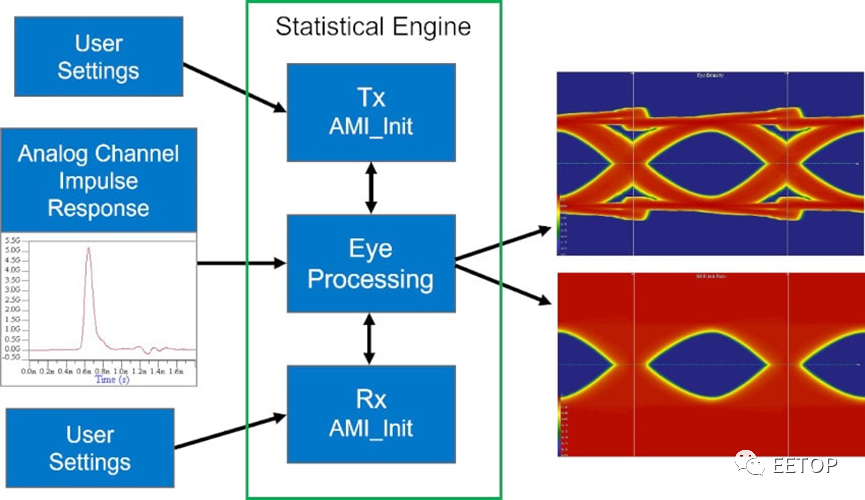

IBIS 模型已用于多代 DDR 系统,支持端到端系统仿真,但从 DDR5 开始添加 EQ 功能和 BER 眼图模板要求,人们寻求新的仿真模型和分析。通过 IBIS-AMI 建模,可以实现快速、准确的 Si 仿真,可跨 EDA 工具移植,同时保护 IO 细节的 IP。IBIS-AMI支持统计和逐位仿真模式,统计流程如下所示。

统计仿真流程

这个流程的结果是一个统计学上的眼图,可用于测量不同误码率水平下的眼图轮廓。

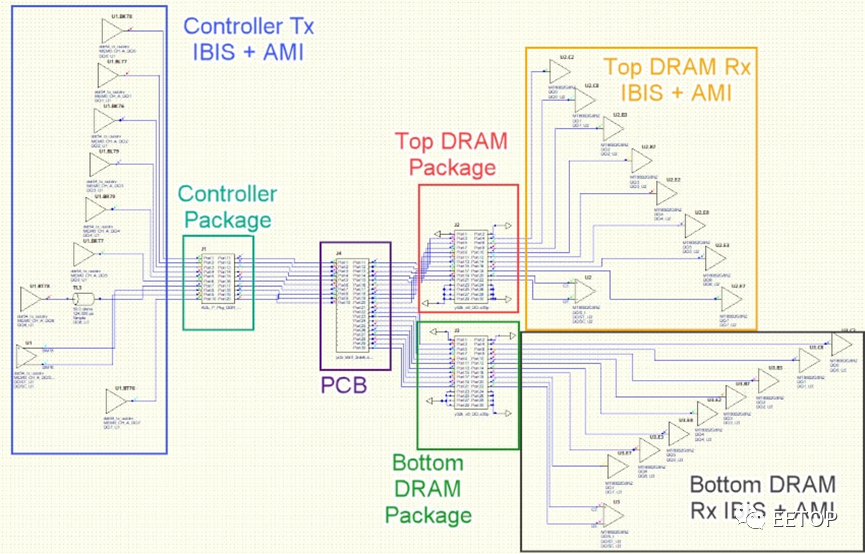

DDR5仿真实例

使用 Micron 提供的 DQ 和 DQS IBIS-AMI 模型在HyperLynx LineSim工具中对 DDR5 仿真进行建模,以下是系统原理图。

DDR5系统原理图

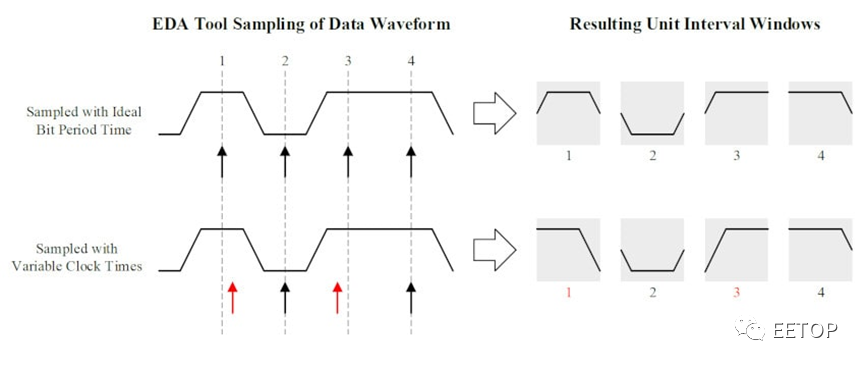

EDA工具在指定的时钟时间捕捉波形,其中时钟时间内的时序不确定性被转移到所产生的输出眼图中,在限幅器及其时钟量化之前重建电压和时序裕量。

Variable clock times

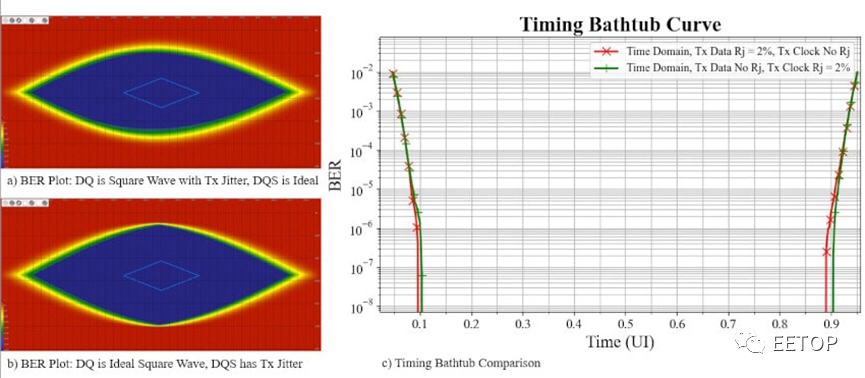

DQS 和 DQ 时序不确定性都会影响眼图,类似于时序裕度。图 A 显示注入到 DQ 信号的抖动,图 B 显示注入到 DQS 信号的抖动。DQ(红色)和 DQS(绿色)抖动一起显示在图 C 中。

Timing bathtub curve

甚至可以对各种组合中的 DQ 信号和 DQS 信号进行正弦抖动效应建模,以查看 BER 和时序浴盆曲线结果。DDR5 具有 Rj、Dj 和 Tj 测量,而不是周期和周期间抖动测量。可以模拟 Rx 和 Rj 值对 BER 图的影响以及bathtub curve时序。

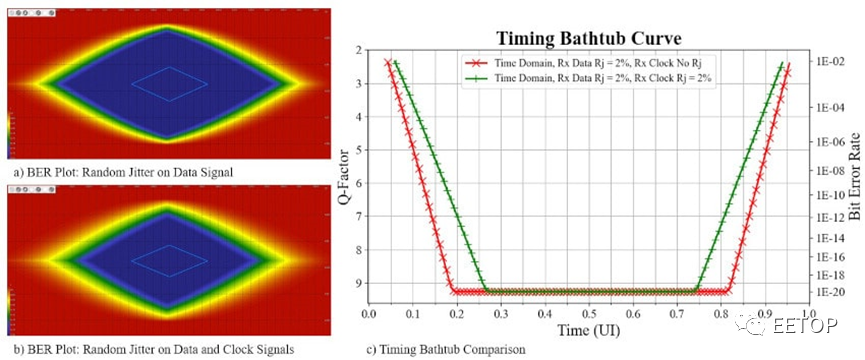

数据上的 Rx Rj 与数据和时钟组合的比较

超越线性和时不变 (LTI) 建模,多重边沿响应 (MER) 技术使用一组上升沿和下降沿。通过定制的高级 IBIS-AMI 流程,它对每个 MER 边缘执行统计分析,然后将组合效果叠加到输出眼图中。

逐位高级仿真结果

在建模中添加 2% 的 Tx Rj 值可显示更真实的 BER 降级图结果。

总结

信号完整性效应主导 DDR5 系统的设计,因此要获得准确的结果,需要对所有新的物理效应进行详细建模。Rx AMI 模型的 IBS-AMI 规范已更新为使用转发时钟。Micron 展示了他们如何使用时钟 DDR5 模拟流程来模拟新效应,包括非 LTI 效应,并实现 1e-16 及以下的 BER 模拟。

关键词: DDR5