台积电技术大秀!揭示最新技术新发展

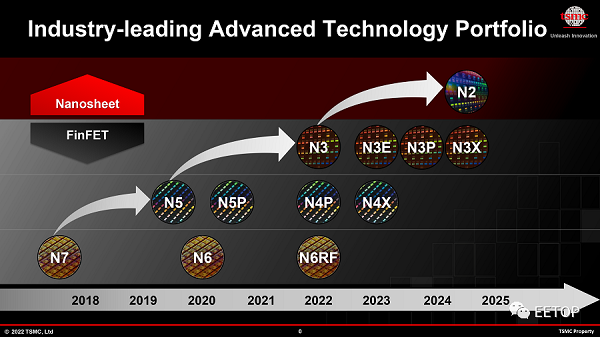

2023-04-27 11:49:43 EETOP台积电在美国当地时间26 日举办2023 年北美技术论坛,会中揭示其最新的技术发展,包括2纳米技术进展,及业界领先的3纳米技术家族新成员,以提供广泛的技术组合满足客户多样化的需求。其中包括支持更佳功耗、效能与密度的强化版N3P 制程、为高效能运算应用量身打造的N3X 制程、以及支持车用客户及早采用业界最先进制程技术的N3AE 解决方案等。

台积电总裁魏哲家表示,台积电的客户从未停止寻找新方法,以利用芯片的力量为世界带来令人惊叹的创新,并创造更美好的未来。凭借着相同的精神,台积电也持续成长进步,加强并推进我们的制程技术,提高效能、功耗效率及功能性,协助客户在未来持续释放更多的创新。

1. 更广泛的3纳米技术组合,包括N3P、N3X、以及N3AE。因为随着N3 制程已进入量产,强化版N3E 制程预计将于2023 年量产,台积电推出更多3纳米技术家族成员以满足客户多样化的需求。

N3P 预计于2024 年下半年进入量产,相较于N3E,在相同漏电下,速度增快5%。在相同速度下,功耗降低5~10%,芯片密度增加4%。

N3X 着重于效能与最大时脉频率以支持高效能运算应用,相较于N3P,在驱动电压1.2伏特下,速度增快5%,并拥有相同的芯片密度提升幅度,预计于2025 年进入量产。

N3AE 将提供以N3E 为基础的汽车制程设计套件(PDK),预计于2023 年推出,让客户能够提早采用3纳米技术来设计汽车应用产品,以便于2025 年及时采用届时已全面通过汽车制程验证的N3A 制程。

2.纳米技术开发进展良好。台积电2纳米技术采用纳米片晶体管架构,在良率与元件效能上皆展现良好的进展,将如期于2025 年量产。相较于N3E,在相同功耗下,速度最快将可增加至15%。在相同速度下,功耗最多可降低30%,同时芯片密度增加大于15%。

3. N4PRF 推进CMOS 射频技术之极限。在2021 年推出N6RF 技术后,台积电进一步开发N4PRF,此为业界最先进的互补式金属氧化物半导体(CMOS) 射频技术,以支持Wi-Fi 7 射频系统单芯片等数位密集型的射频应用。相较于N6RF,N4PRF 逻辑密度增加77%,且在相同速度下,功耗降低45%。

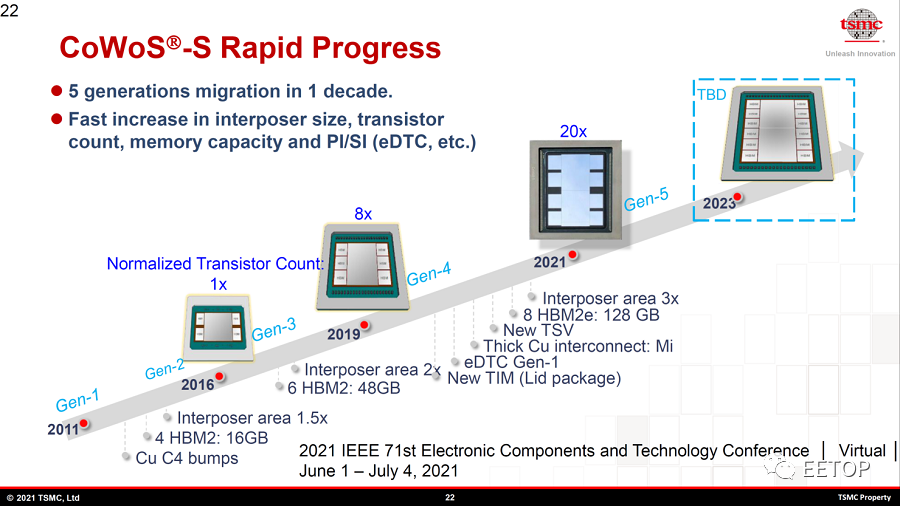

4. TSMC 3DFabricTM 先进封装及硅晶堆叠。台积电3DFabric系统整合技术之主要新发展包括:

先进封装:为了满足高效能运算应用在单一封装中置入更多处理器及存储器的需求,台积电正在开发具有高达6 个光罩尺寸(约5,000 平方毫米) 重布线层(RDL) 中介层的CoWoS 解决方案,能够容纳12 个高频宽存储器堆叠。

三维芯片堆叠:台积电宣布推出SoIC-P,做为系统整合芯片(SoIC) 解决方案的微凸块版本,提供具有成本效益的方式来进行3D 芯片堆叠,SoIC-P 加上目前的SoIC-X 无凸块解决方案,使得台积电的3D IC 技术更臻完善。

设计支持:台积电推出开放式标准设计语言的最新版本3DbloxTM 1.5,旨在降低三维集成电路(3D IC) 的设计门槛。3DbloxTM 1.5 增加了自动凸块合成的功能,协助芯片设计人员处理具有数千个凸块的复杂大型芯片,可缩短数个月的设计时程。

另外,台积电技术论坛后续将陆续在包括美国奥斯丁、波士顿、欧洲、以色列、中国大陆、以及日本举行。其中,5/11 将移师台北举办。