ADC、DAC、PLL、SerDes 工艺节点案例分析

2022-12-30 12:29:07 EETOP传感器本质上是模拟的,它们通过使用模数转换器 (ADC) 块进行数字化处理。在最近的IP SoC活动中,国外科技媒体semiwiki有机会了解到Alphacore首席运营官Ken Potts关于他们的 ADC 半导体 IP 的演讲。Alphacore 于 2012 年成立,是总部位于亚利桑那州的全球组织,主要为 AMS、射频、成像和抗辐射电子产品提供标准和定制 IP。

数据转换器可以在任何 IC 工艺节点中设计,但是 FD-SOI 技术提供最低的功率,同时可以承受辐射效应。与体 CMOS 工艺相比,28 纳米 FD-SOI 芯片的功耗将降低 70%。

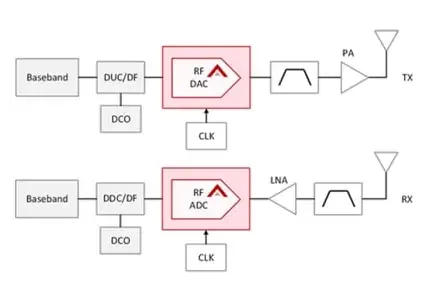

射频数据转换器需要同时具有高带宽和低功耗,以适应相控阵架构、直接射频采样、波束成形和 5G 无线电等应用。

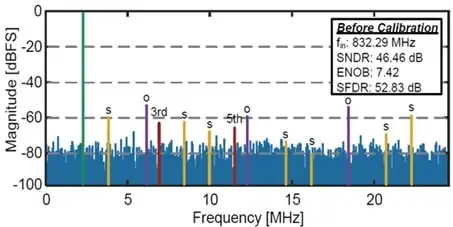

Alphacore 采用 GlobalFoundries 的 22nm FD-SOI 工艺设计了一款名为 A11B5G 的混合 ADC,采样率为 5GS/s,分辨率为 11 位,电源电压为 800mV,功率仅为 50mW。该 ADC 的一个有用特性是集成自动校准,因为它消除了交错杂散。

校准前输出频谱

校准后去除杂散

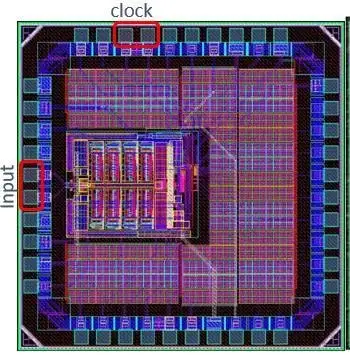

另一个功耗更低的模数转换器是 A10B3G,采样率为 3GS/s,100MS/s 时有效位数 (ENOB) 为 8.6,功耗仅为 13mW,采用 GlobalFoundries 的 22nm FD-SOI 工艺制造。

A10B3G ADC

Ken 展示的第一款低功耗数模转换器 (DAC) 是 D6B5G,它的功耗仅为 16mW,具有 5.4 ENOB、6 位输入并以 5GS/s 的速度运行。

锁相环(PLL) 电路可用于解调信号、在 SoC 内部分配时钟信号、创建新的时钟频率倍数或从通信通道恢复信号。PLL5G 是一种极低抖动 <150fs 的设计,于 2023 年 1 月在 22FDx 节点中流片。

对于串行通信,使用了 SerDes 电路,Alphacore 有一个基于 22FDx 的设计于 2023 年 1 月流片,称为 SD16G,支持从 1Gb/s 到 16Gb/s 的数据速率,使用 8 或 16 位进行序列化/去中心化-序列化宽度。支持所有流行的协议:PCIe、JESD204、SATA、SRIO、SG-MII、USR/XSR。

四个代工节点共享了 ADC、DAC、PLL 和 SerDes 的路线图:TSMC 28HPC+、TSMC 12FFCP、Intel16、GF 22FDx。因此,2023 年对于经过硅验证的 IP 来说是非常繁忙的一年。

Alphacore是设计抗辐射电路的专家,特别关注总电离剂量 (TID) 和单粒子效应 (SEE) 等效应。他们现在在 GF 22FDx 中有抗辐射 ADC 和 DAC,然后计划在 Q2'23 中使用 Intel16,在 Q3'23 中使用 GF 22FDx,在 Q4'23 中使用 SkyWater RH90。

另外三个抗辐射设计示例是电源管理 IC (PMIC)、2 色像素内 ADC 和具有 120 FPS 高帧速率的成像器/相机。

低功率和抗辐射应用是一个利基市场,需要专业知识。Alphacore 在提供不断增长的 ADC、DAC、PLL、SerDes、PMIC 和成像器系列方面有着良好的记录。2023 年的流片时间表看起来很满,这意味着您将获得更多经过硅验证的 IP,可用于您在 5G、太空通信、汽车甚至量子计算领域的设计。

原文

https://semiwiki.com/ip/321611-analog-to-digital-converter-circuits-for-communications-ai-and-automotive