台积电为新工艺节点颁发EDA认证

2022-11-07 13:03:46 EETOP为了确保设计人员拥有合适的EDA工具来完成更先进节点的芯片设计,台积电宣布了一系列针对其最先进工艺的 EDA 工具认证——包括从 3 纳米节点到 3D IC集成。

随着 N3E、N4P 和 3DFabric 工艺的发布,新的独特设计要求进行新的认证,以确保同时满足设计人员的系统要求和 TSMC 的工艺要求,从而缩短上市时间。

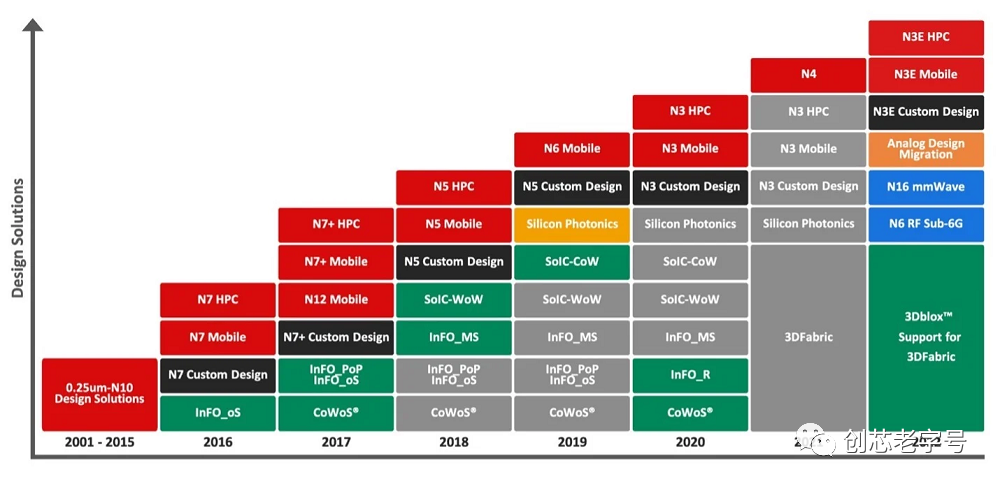

台积电设计解决方案随着时间的推移而发展,提供了越来越多的技术来满足各种设计需求。图片由台积电提供。

在本文中,我们将简述台积电的先进工艺及其影响,然后对台积电授予的认证以及这些认证如何帮助未来的设计人员的做一个简要介绍。

保持进步

台积电延续了晶体管更小、更密集的趋势,此前已宣布其 最新的数字节点N3E 和 N4P,以使设计人员能够跟上减小整体 IC 尺寸的步伐,为相同尺寸的晶圆上的附加功能创造更多空间。这两个节点都是现有技术的扩展,但与原始节点相比提供了增强的性能。

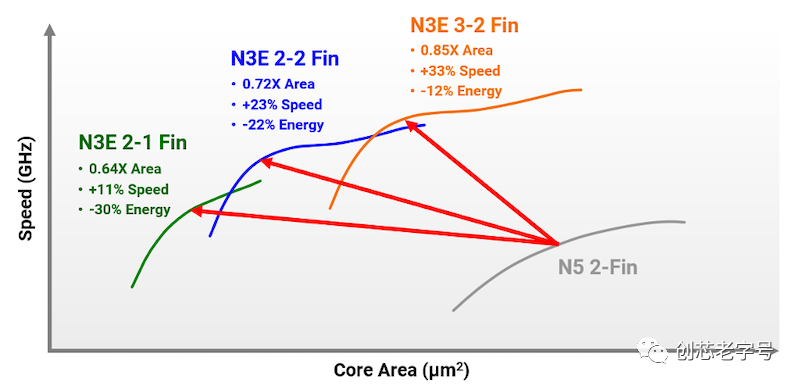

N3E技术是一种 3 纳米“增强型”技术,与以前的技术相比,在速度和功耗方面都有了显著提高。此外,根据特征尺寸以自定义方式实施 FinFET的自由度允许在速度、面积和效率方面进行最佳权衡。

N3E 工艺变化提供给设计人员以提高性能与功耗。图片由台积电提供

N4P技术,4nm工艺,同样是N4平台的延伸。附加一个“P”表示性能,与 N5 平台相比,N4P 工艺的性能提升 11%,比 N4 平台提升 6%。N4P 平台专为轻松从基于 5 nm 的设计迁移而构建,使设计人员能够轻松地提高其设计的性能。

最后,为了避免 摩尔定律的终结,台积电还为其 3DFabric 工艺授予了认证:该技术旨在将 IC 设计领域从主要的平面视角转变为立体视角。使用 3DFabric,感兴趣的设计人员可以为他们的项目添加另一个维度,允许使用 TSMC 的 硅堆叠和先进封装技术进行更广泛的集成,同时保持目标板上相同的占用面积。

为设计找到合适的EDA

尽管一些工程师可能相信他们设计电路的能力,但我们确实需要某种自动化或仿真来验证复杂的设计。为了确保 EDA 工具不仅满足设计人员的需求,而且满足工艺流程的需要,台积电成立 了 EDA 联盟,直接与 EDA 工具供应商合作。

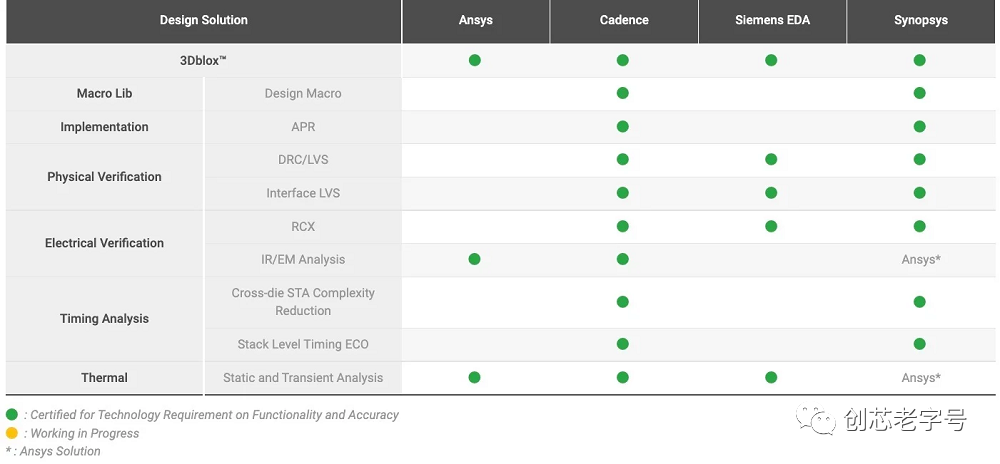

EDA联盟共有16个合作伙伴,包括Cadence、Siemens、Ansys和Synopsys。这些小组中的每一个都提供了与 TSMC 工艺兼容的 EDA 工具,范围从 物理验证到 时序和 power signoff。为了确保兼容性并缩短上市时间,台积电已发布认证,以向设计人员保证他们的 EDA 工具符合台积电的内部要求。

截至 2022 年 10 月 26 日的 3DFabric EDA 工具认证状态。图片由 台积电提供。

台积电主要致力于为其先进节点N3E、N4P和3DFabric颁发认证。根据特定的应用,某些EDA工具可能提供改进的功能或更好的性能。尽管EDA工具的产品数量很多,但设计师可以放心,只要他们想要的工具经过认证,就可以保证与台积电的高级节点正常工作。

对你的定制设计充满信心

随着摩尔定律不可避免的终结比以往任何时候都更近,高性能的先进节点和3D集成等新的设计方法变得比以往任何时候都更重要。然而,如果没有适当的EDA支持,设计人员的工作将变得越来越困难。

台积电直接与EDA公司合作的先例标志着自上而下支持网络在设计界的有利趋势,减少了EDA工具的开发时间,允许设计师尽快开始进行下一代设计,而不必担心他们没有合适的工具。