《芯片验证从入门到精通》75折福利补贴券最后3天倒计时!

2022-10-18 14:00:53 EETOP注:本课程只针对对自己目前技能有提升需求的理工科本科及以上学历的同学。试听部分内容涵盖数字芯片验证工程师产业链相关职业岗位,所需掌握的技能,验证流程,验证效率的提升等相关内容。

同学们可以先从试听部分了解清楚了是否契合自己的需求再进行报名。

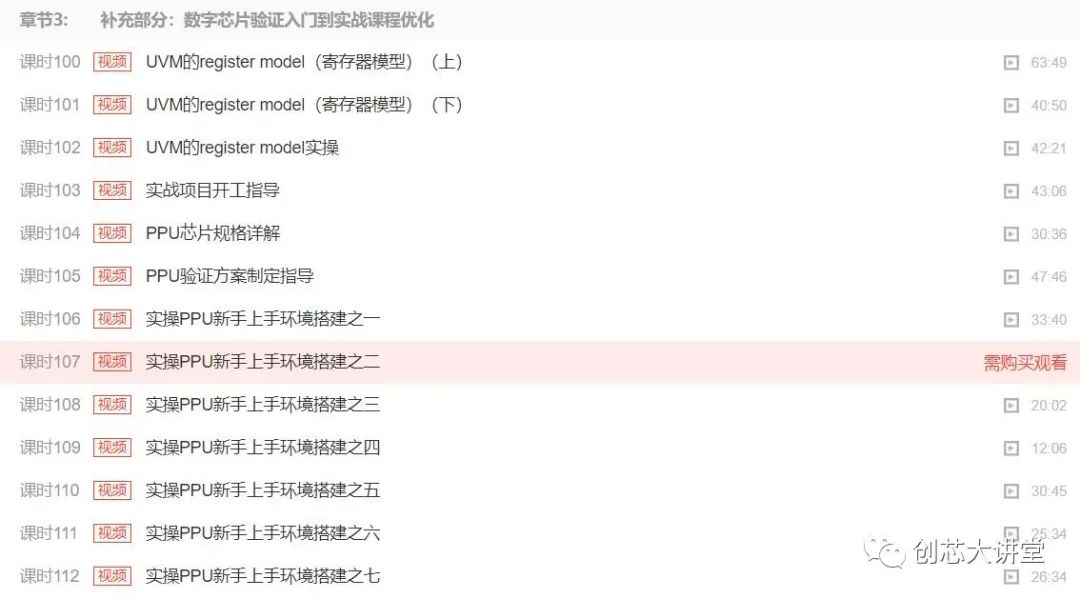

虽然创芯大讲堂《芯片验证从入门到精通》99课时已经全部更新完毕,但是在很多同学的建议下我们陆续对之前的课时做了优化工作,目前又新增了16课时作为补充,总课时达到115课时(且优化部分还在持续更新中。。)

之前学过课程的小伙伴可以继续在后面的课时中找到课程优化部分相对之前的内容对比学习。

特比提示:课程加量后价格保持不变!目前正在做限时75折优惠,目前已进入倒计时阶段。感兴趣的欢迎抓紧购课!

补充部分:数字芯片验证入门到实战课程优化

扫码抢券购买或免费试看

有意向转入IC行业的在职人士。

课程第一部分为《数字芯片验证通识》本部分我们已全部为大家开放为免费学习,总共3个学时。

课程第二部分为《Verilog HDL入门》共18个课时

课程第三部分为《System Verilog入门》共18课时

课程第四部分为《UVM验证入门》共23个课时

课程第五部分为《实验训练总结》共33个课时

课程理论部分

本课程讲师曾就职于知名大厂,数字芯片验证经验丰富,经过多年的基层编码以及一流研发体系的训练,除了对数字芯片验证技能有深刻的见解,另外对芯片设计验证研发体系也了然于心。因此本课程的实训项目,借鉴知名大厂实训项目,整个实操通过一个完整的实例搭建,包括测试点分解、前端设计代码的书写、验证平台的搭建,以及每个阶段一系列研发文档的输出、实操环节,让学员掌握数字芯片流程中的每个环节,最终通过覆盖率的收集,检查项目验证的完备性,最终达到对芯片验证入门上手的效果。

| 课程大纲 | 内容简介 | |

| 1 | 数字芯片验证通识 (8课时) | 第4讲开展数字芯片验证工作——上手操作一个简单的数字芯片验证过程 第7讲数字芯片验证基本技能——inux基础Vi编辑基础知识 第8讲数字芯片设计基本技能——She常见指令与gvim编辑器实操演示 |

| 2 | VerilogHDL入门 (17课时) | 第9讲VerilogHDL设计module结构分解认知 第10讲表达式操作符与操作数详解 第11讲VerilogHDL组合逻辑实现方式讲解与EDA实操(上) 第12讲VerilogHDL组合逻辑实现方式讲解与EDA实操(下) 第13讲VerilogHDL时序逻辑实现与EDA实操(上) 第14讲VerilogHDL时序逻辑实现与EDA实操(上) 第14讲VerilogHDL条件语句详解 第15讲VerilogHDL门级建模、数据流建模、行为级建模讲解与EDA实操 第16讲系统任务与系统函数以及codingstyte 第17讲高性能电路设计 第18讲数字电路复位 第19讲状态机(上) 第20讲状态机(下) 第21讲时序与时钟 第22讲异步时钟域的同步处理方式 第23讲握手协议详解 第24讲FIFO设计 第25讲低功耗设计有哪些? |

| 3 | SystemVerilog入门 (18课时) | 第26讲SystemVerilog数据结构:数组、队列、结构体、枚举等讲解 第27讲SystemVerilog数据结构:数组、队列、结构体、枚举等调用函数EDA实操 第28讲SystemVerilog面向对象在验证中的应用——封装、继承、多态(上) 第28讲SystemVerilog面向对象在验证中的应用——封装、继承、多态(下) 第30讲SystemVerilog随机以及随机化的对象 第31讲SystemVerilog约束以及约束的对象 第32讲SVA讲解 第33讲SVA实操练习 第34讲覆盖率 第35讲覆盖率驱动验证 第36讲线程的概念 第37讲旗语和信箱简介 第38讲SystemVerilog验证平台简介 第39讲SystemVerilog中激励的发送 第40讲SystemVerilog中Checker的建立 第41讲SystemVerilog封装在tb中的应用 第42讲标准SV验证平台搭建 第43讲功能覆盖率的建立 |

| 4 | UVM验证入门 (23课时) | 第44讲什么是UVM,UVM与验证的关系 第45讲初步认识一个UVM验证环境 第46讲驱动设计——uvm_driver 第47讲interface和transaction的作用 第48讲env的在环境中的作用 第49讲monitor和agent的在环境中的作用 第50讲rm和scoreboard的的作用 第51讲sequence和sequencer的的作用 第52讲configuration和factory机制 第53讲TLM通信机制简介port和export 第54讲IMP的通信方式 第55讲FIFO的通信方式 第56讲uvm的phase机制 第57讲sequencer和driver的通信机制 第58讲如何发送sequence 第59讲UVM寄存器模型 第60讲前门访问和后门访问 第61讲实操UVM验证环境打印debug信息 第62讲实操激励的产生以及修改随机和约束 第63讲实操组件的配置 第64讲实操采样设计信号以及做checker 第65讲实操sequence的发送机制 第66讲实操寄存器模型 |

| 5 | 实验训练总结 (30课时) | 第67讲实训PPU项目芯片规格熟悉(上) 第68讲实训PPU项目芯片规格熟悉(下) 第69讲实训PPU项目设计代码结构分析 第70讲什么是测试点 第71讲实训PPU项目测试点提取 第72讲实训PPU项目验证方案 第73讲实训PPU项目初始环境搭建 第74讲实训PPU项目环境冒烟 第75讲实训PPU项目补全driver组件 第76讲实训PPU项目补全monitor、agent、env组件 第77讲实训PPU项目补全scorboard、referencemodel组件 第78讲实训PPU项目补全sequence和testcase 第79讲实训PPU项目代码覆盖率分析 第80讲实训PPU项目功能覆盖率 第81讲cornercase的补充与完善 第82讲验证报告的书写(上) 第83讲验证报告的书写(下) 第84讲PPU项目验证总结,问题回溯 第85讲IIC实训项目规格讲解 第86讲如何开展相关协议的学习 第87讲IIC实训项目设计代码结构分析 第88讲提取IIC的测试点 第89讲IIC验证方案指定 第90讲IIC验证仿真环境搭建(上) 第91讲IIC验证仿真环境搭建(中) 第92讲IIC验证仿真环境搭建(下) 第93讲IIC环境冒烟 第94讲IIC的case补全 第95讲IIC的覆盖率驱动验证流程 第96讲IIC补全case 第97讲IIC验证报告 第98讲IIC芯片验证总结 第99讲数字芯片设计验证关键知识点总结 |

VIP学习指导群进入方式:购买课程后,添加微信ssywtt即可拉入群

购课后的同学对课程的质量好评如潮

特别提醒!!

购买之前可以添加微信ssywtt咨询,购买之后可进到课程VIP技术及就业指导群。为保证辅导质量,本期VIP群每期仅限50人学习。

注意:为防止盗版及非法交易,购买本虚拟产品不支持退款,请购买前一定先试看,并且建议进入课程售前群咨询是否建议购买。

扫描上方二维码,优惠购买课程或免费试看

关于购课特别提示

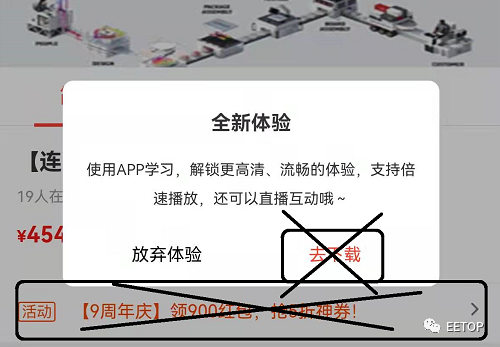

请不要点击:去下载 以及推荐的红包 活动!