潜力巨大!新型自适应晶体管可使芯片晶体管使用量减少85%

2021-12-28 13:14:59 EETOP

晶体管——尤其是场效应晶体管(FET)——是半导体设计的基本单元:三个要素协同工作,开启我们的技术体验。。就像水闸控制水是否流动一样,晶体管控制电流是否从源极流向漏极。然而,晶体管本身并不十分聪明;事实上,如果没有其控制电极的输入,它将变得毫无用处。延伸水的比喻,只有当你能控制水是否流经它时,水坝才会非常有用。因此,我们需要第三个基本元素--晶体管的门极。晶体管的这种三要素的简单性使我们能够将数十亿个晶体管塞进最新的高性能芯片中虽然晶体管可以承担许多不同的功能,但这些功能本身是简单的。正是由于在集成电路中添加了许多小型、简单的晶体管,才能够实现更高阶的性能和更复杂的工作负载。一定数量的晶体管,按一定的方式排列,可以变成Zen 3内核;也可以变成Nvidia CUDA内核或额外的内存缓存块。

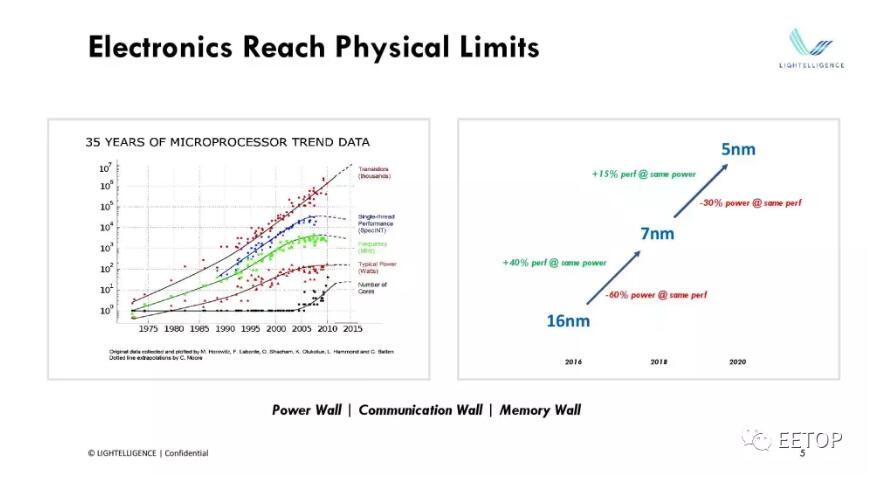

还记得英特尔的tick-tock策略吗?在这些方面,一个时钟(tock)(微架构变化)本质上对应于可以通过重新排列和重新设计晶体管块来解锁的性能改进。一个滴答声(tick)(制造节点的变化)增加了可用于工程师日益复杂的电路的晶体管数量。英特尔tick-tock的战略的死亡表明,晶体管密度的提高越来越难以实现。虽然材料和设计研究已经设计出许多改进晶体管的方法,但它们的基本设计保持不变。在缺乏变化的地方,就有机会:重新设计晶体管可以带来什么好处?

“由于适应性增强,以前需要 160 个晶体管的算术运算现在可以使用 24 个晶体管。这样,电路的速度和能效也可以显着提高。” 研究小组的成员Walter Weber 教授解释说。换句话说,新的自适应晶体管可以将给定工作负载所需的晶体管数量减少多达 85%。此外,由于用于相同工作的晶体管数量更少,整个设计中的功耗、温度和泄漏点都会降低——这反过来又会允许更高的频率缩放和性能。

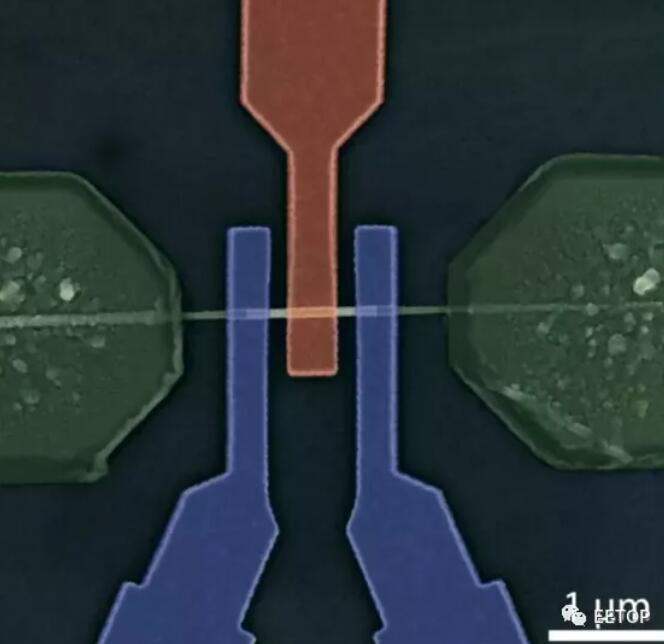

"我们用一根极细的锗线,通过极其干净的高质量接口连接两个电极,"研究小组的成员Masiar Sistani博士解释说。"在锗段上方,我们放置了一个像传统晶体管中的栅极电极。决定性的是,我们的晶体管在锗和金属的界面上还有一个控制电极。它可以对晶体管的功能进行动态编程"。

研究团队成员:Walter Weber, Masiar Sistani and Raphael Böckle(从左到右)

"我们之所以使用锗,是因为锗有一个决定性的优势,具有一个非常特殊的电子结构:当你施加电压时,电流最初会增加,正如你所期望的那样。然而,在某个阈值之后,电流再次减少--这被称为负差分电阻。在控制电极的帮助下,我们可以调节这个阈值在哪个电压上。这导致了新的自由度,我们可以用它来赋予晶体管我们目前所需要的特性。"

令人惊讶的是,这项技术承诺可快速扩展和部署:所使用的材料都不是半导体行业的新材料,也不需要新的专用工具。当然,任何最初的采用都将受到限制,而且研究人员相信他们的自适应晶体管将作为附加器件被纳入某些半导体设计中,以便在需要时加以利用。