Libre-SOC首款ASIC测试芯片将采用180nm工艺制造

2021-07-09 10:36:07 cnBeta.COM

尽管与当前已问世的图形处理器相比,它不见得是运行速度最快的。但作为一个 CPU / GPU 混合项目,Libre-SOC 最大的特点,就是做到了软硬件层面的完全开源。

具体说来是,为了实现图形加速,Libre-SOC 在 Power 芯片基础上,使用了类似 Mesa 的 OpenGL / Vulkan 软件实现方案。

据悉,除了 Chip4Makers 和索邦大学的合作,这个充满雄心壮志的开源硬件项目,还得到了 NLNet 等机构的资助。

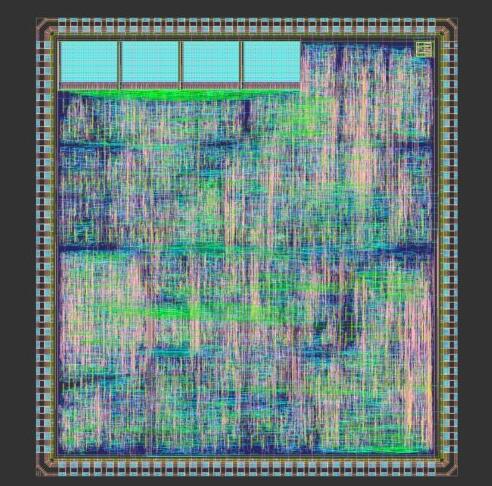

现阶段的 Libre-SOC 拥有 13 万门(130k gates),大小为 5.5×5.9 mm²,且已实现 v3.0B 版本的 OpenPOWER ISA 定点子集。

最后,在该芯片被用于混合型 CPU-VPU-GPU 之前,它将先在台积电 180nm 工艺基础上,使用 IMEC 的 MPW 实验性服务进行多次测试制造。

免责声明:本文由作者原创。文章内容系作者个人观点,转载目的在于传递更多信息,并不代表EETOP赞同其观点和对其真实性负责。如涉及作品内容、版权和其它问题,请及时联系我们,我们将在第一时间删除!