Intel:未来封装的巨变

2019-07-15 10:13:50 semiwiki 翻译:半导体百科然而,至少对我来说,并不清楚的是,这些产品会被多迅速的接受,以及客户会如何激进的扩大设计架构的多芯片整合空间。最近,我有机会参加由英特尔举办的高级封装研讨会,会后我认为:业界对高级MCP设计的计划将急剧加速。

在研讨会上,关于这项技术发展最引人注目的迹象,是英特尔封装/测试技术开发(ATTD)副总裁Ram Viswanath的发言,他说 "我们开发了独特的3D和2.5D封装技术,并且我们渴望与客户分享。产品架构师现在有能力追求具有前所未有的规模和功能多样性的MCP。"这是出人意料的发言, 一些会员甚至要求Ram给予确认。毋庸置疑,世界上最大的半导体IDM正热情地与客户一起寻求MCP设计合作。

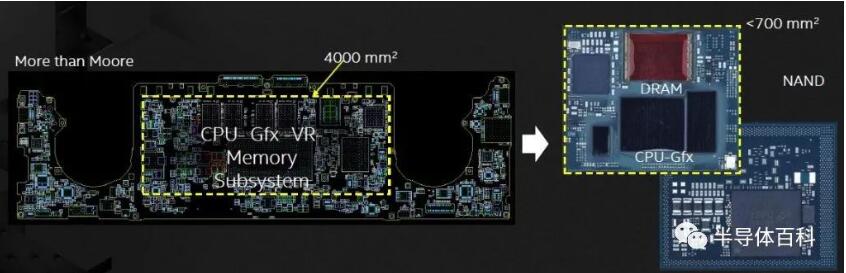

例如,下面的概念图呈现了把CPU,GPU,VR加速器和存储器架构封装到一个仅占原独立元件封装方法六分之一大小的空间,原封装的尺寸有可能很大 - 会高达100mm x 100mm。(英特尔Xeon系列的Cascade Lake服务器模块是一个76mm x 72.5mm的MCP,包含两个"全刻度尺寸"处理器芯片。)

对于保守的读者来说,这与前段时间英特尔宣布刚刚起步的代工厂服务带来的感觉是完全不同的。这里传达了一个清晰的,简明扼要的信息 - 新兴的数据驱动应用程序将利用多芯片封装集成技术(围绕英特尔CPU或FPGA),英特尔ATTD业务部门会致力于支持这些独特的客户设计。

下面将介绍一些英特尔MCP的历史,和2.5D和3D封装技术的细节,以及一些正在进行中的对未来封装技术的研究

MCP History

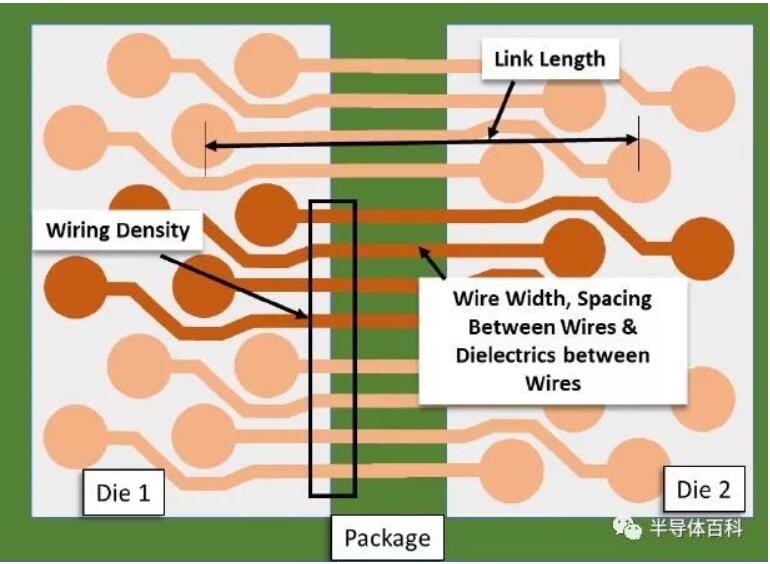

研讨会结束后,我随访了Ram V.,,他对英特尔MCP技术的研发有丰富的见解。他说,"英特尔在多芯片封装方面拥有大量的经验。例如,我们正在推出一项独一无二的嵌入式硅桥技术,用于芯片间封装连接,已经研发了十多年。这种技术能做到芯片间宽接口连接,且具有低pJ/位功耗,以及芯片间低信号损耗和低成本的特性。"下图描绘了相邻芯片边缘的bump块之间的互连迹线- 一个关键指标是 (bump的密度和平均die周长内可绕线的迹线长度)

“技术开发的重点是将硅桥嵌入基于面板的有机封装组装流程中。桥接线的位置和角度要求非常苛刻。“,Ram继续说道。

Ram展示了采用嵌入式桥接器的带有HBM内存的Stratix FPGA模块的示例。“此产品路线图始于英特尔在收购之前制造Altera FPGA时的几个SKU。自那时以来,FPGA应用已经大幅增长 - 现在整个Stratix产品线都有MCP产品。“他还展示了(未封装的)最近宣布的带有外部GPU的Kaby Lake CPU模块的示例,利用芯片之间的嵌入式桥接器。

"对于来源于不同代工厂的芯片是否有明显的封装或可靠性问题?",我问道

"这项技术本就是与供应商合力开发的成果"他指着各种MCP模块中的不同芯片继续说,"这个是来自台积电,这个是来自GF,这些是来自SKHynix的HBM内存堆栈。我们与全部的供应商都密切合作,制定了bump冶金规格和材料体积,BEOL介电材料特性,芯片厚度和翘曲度,所有这些芯片的都被证明是合格的。"

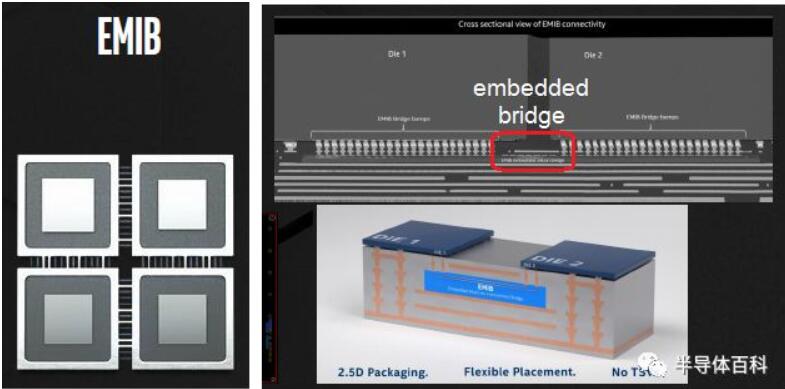

EMIB

嵌入式多管芯互连桥(EMIB)是用一小块硅在MCP中的两个管芯的相邻边缘之间提供自由的互连性。 EMIB目前集成了四个金属化平面--2个信号和2个电源/地(主要用于屏蔽,但也可用于芯片之间的P / G分配)。

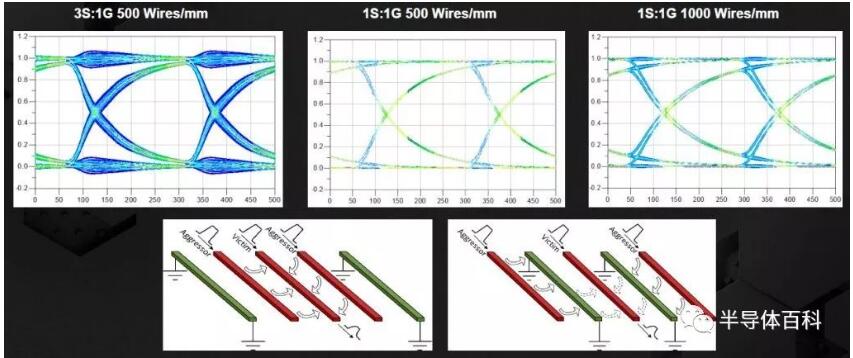

此外,英特尔的Si团队分析了不同长度的信号和接地走线的不同互连拓扑的信号损耗 -请参见下图。

英特尔研究员Ravi Mahajan提供了有关EMIB的其他技术信息。他指出EMIB平面的金属厚度介于硅片RDL层和封装迹线之间,实现了互连间距和损耗特性之间的平衡。“我们现在是2um的线宽和2um线间距,并朝着1um 线宽和 1um线间距努力。我们对EMIB的Si分析表明,长达8mm的长度仍能提供足够的眼图余量。从概念上讲,EMIB可以达到~200平方毫米。“(例如,相邻芯片边缘之间的距离为25 mm,宽度为8 mm)

目前,桥接器的设计和制造由英特尔ATTD完成 - 本身没有外部设计套件。“在ATTD上嵌入式桥接器的相邻芯片的I / O焊盘平面图的开发是一项协作努力。”,Ram表示。“在VDD IO和GND IO的设计上也考量了从整个封装到EMIB周围及芯片上的周边bump阵列的电压传输。英特尔ATTD还对复合封装设计进行了热和机械完整性分析。由于MPC新兴市场的散热水平可能很高,并且由于芯片与EMIB硅和有机基板之间的热膨胀系数不同,因此bump接触面的热与机械性能分析至关重要。

显而易见但值得一提的是,封装中EMIB硅的存在不会干扰将表面贴装无源元件添加到整个组件的传统工艺(例如,去耦帽)。在研讨会上,对背面封装金属环电感器和SMT帽的支持得到了强调 - “自22nm工艺节点以来,英特尔CPU封装集成了电压调节和电压域控制。封装上的电感和电容元件是稳压器设计中使用的降压转换器的一部分。“,Ram指出。和英特尔合作设计MCP的客户也可以获得此功能支持。

基于EMIB的设计的特性与使用硅中介层的2.5D封装产品有很大不同。一方面,由于介质层跨越整个组件,因此Si介质层赋予了芯片间连接更大的灵活性。(较新的2.5D产品提供“缝合”光罩曝光之间的连接迹线工艺,以提供大于1X最大光罩场尺寸的介质层设计。)相反地,EMIB方法专注于相邻芯片边缘(宽,平行)连接。在研讨会中提到,将多个桥接器集成到传统封装组件和最终封装流程中使得100mmx100mm 介质层尺寸在500mm×500mm有机基板面板上成为可能。具有有机基板的EMIB实现了可观的成本优化

3D “Foveros”

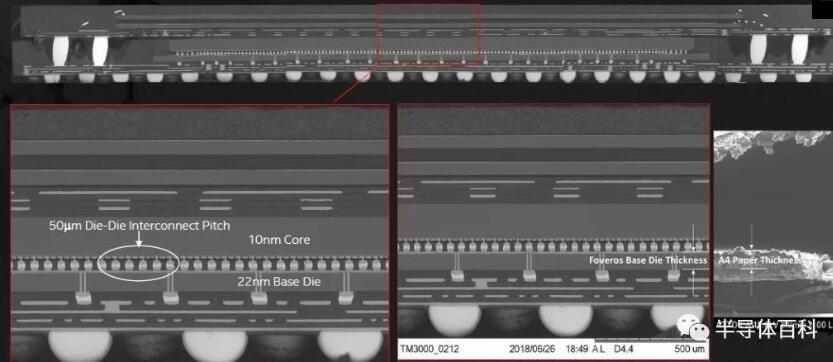

借助Lakefield CPU产品系列,英特尔推出了采用硅通孔的3D芯片堆叠封装产品。下图说明了3D芯片堆栈。

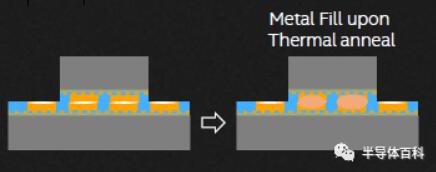

高级封装研发的重点是减少TSV和微凸起的节距大小 - 目前的节距为50um,目标是为30-35um。这将需要从热压粘合转变为独特的“混合粘合”工艺 - 见下图。

热压结合利用压力和温度来融合两个模面上的裸露焊盘冶金,而混合结合始于(有些深奥的)抛光工艺,以在模具表面提供具有几纳米精确控制的“凹陷”的焊盘金属。结合步骤利用(亲水的,极端平面的)模具表面之间的范德华力,然后在退火过程中使金属膨胀以产生焊盘连接。

另一个关键的3D封装研发关注重点是压缩芯片厚度- 高级3D封装的目标是极力压缩最终组件的厚度。“堆叠芯片的薄化加剧了装配和可靠性问题。”,Ravi M.强调说。他举了一个有趣的视觉例子,“考虑到比一张A4纸更薄的芯片的操作和翘曲要求。”(起始300mm晶圆厚度:~775um; A4纸张厚度:~50um)

在不久的将来,将多个3D芯片组合作为大型2.5D拓扑的一部分的能力将被提供,配置Intel ATTD表示为“co-EMIB”。下图说明了3D堆叠芯片与堆叠之间嵌入式桥接的组合概念。

Chiplets, KGD’s, and AIB

MCP技术的加速采用将依赖于广泛的芯片组供应,其方式类似于SoC中的硬IP功能。如上所述,英特尔ATTD团队已经解决了主要硅源的物理材料问题,以确保高组装/测试产量和可靠性。然而,小芯片I / O之间的电气和功能接口定义需要在整个行业范围内集中精力进行标准化,以确保芯片级的互操作性。

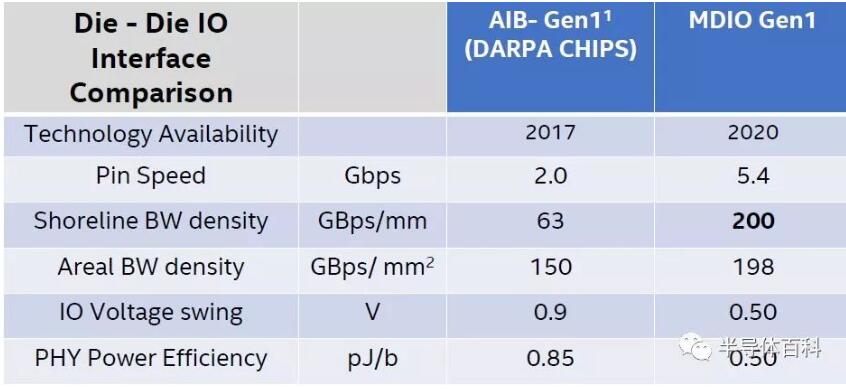

英特尔已发布了AIB规范,并且是DARPA“CHIPS”计划的积极参与者,以推广芯片级标准。(DARPA链接,AIB链接 - 需要注册)有些令人惊讶的是,IEEE似乎没有积极参与这项标准活动 - 很快,毫无疑问。

在研讨会上,英特尔ATTD团队表示,下一代芯片级接口规范(MDIO)正在进行内部活动,目标是将数据速率从2Gbps提高到5.4Gbps(在较低的电压摆幅下优化功率)。

MCP产品设计将继续进行,但采用的增长需要一个明确的标准 - “用于小芯片互连的以太网”,正如DARPA的Andreas Olofsson所描述的那样。

基于芯片的设计还有另一个方面,在研讨会上进行了简要讨论。 MCP的最终后烧入测试产率将取决于已知良好裸片(KGD)小芯片的测试和可靠性特征。 ATTD团队表示,英特尔已对生产ATE设备开发进行了长期(内部)投资。突出的一个特定功能是能够在晶圆级执行加速温度循环测试,快速识别/分类早期失效– 以避免运送到封装组装的KGD在最终老化后不会产生大的良率损失。小芯片“IP”的供应商当然也需要以低测试成本解决如何提供高可靠性芯片的问题。

Futures

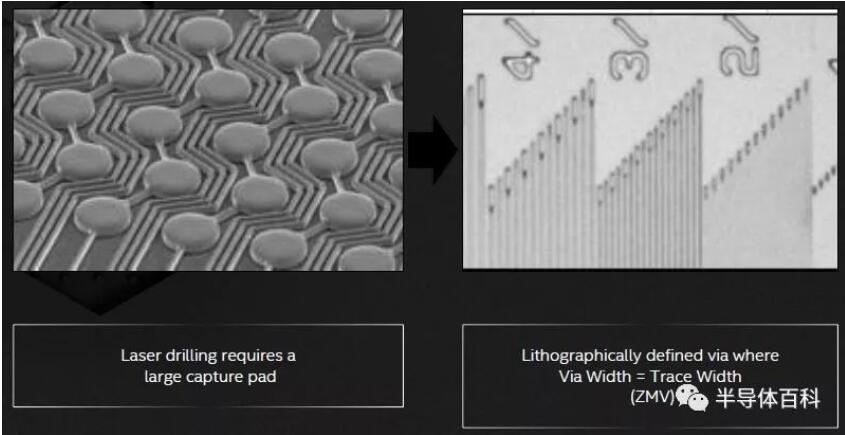

最后的研讨会演讲来自英特尔研究员Johanna Swan,他介绍了一些正在进行的高级封装研发。最引人注目的机会是把迹线连接变成到通孔连接的工艺。不是上图中描绘的大的通孔焊盘到迹线尺寸差异,“零未对准通孔”将使互连密度显着改善。下图说明了当前封装迹线-通孔拓扑,以及2-4um走线宽度的新ZMV迹线连接。

目前基于环氧树脂的封装面板采用激光钻孔 - 实现ZMV,一项新技术正在研究中。(Johanna表示,聚酰亚胺系列的可光成像材料可提供足够高的通孔密度,但材料,工艺和成本限制要求使用环氧树脂面板– 这就需要独特的环氧树脂工艺。)如果ZMV技术转换对于生产,MCP互连(连线+空间)迹线密度将大幅增加- 当与微凸块间距的改进相结合时,在大型MCP中实现的系统级功能将是非常令人印象深刻的。

Summary

研讨会有三个关键要点。

•异构多芯片(芯片和/或小芯片)封装将为系统架构师提供巨大的机会来追求功率/性能/面积+体积/成本优化。

•与采用硅中介层的2.5D封装相比,裸片接口处的英特尔EMIB互连桥提供了一组独特的成本/尺寸/复杂性权衡。

•英特尔ATTD团队致力于为寻求数据驱动市场独特产品解决方案的客户提供先进的2.5D,3D和合并(co-EMIB)技术支持。

坦率地说,在最近的微电子学史上,现在应当是产品架构师工作最有趣的时期。