数据说话:全球最高工艺EUV 5nm--台积电碾压三星!

2019-05-06 13:02:29 EETOP我们将首先回顾一下两家的7nm比较。(可参考:7nm-台积电 VS 三星)

7nm

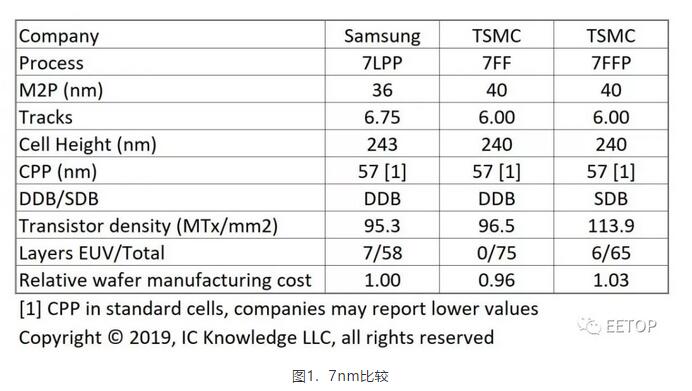

图1 比较了三星的7LPP工艺与台积电的7FF和7FFP工艺。

图1. 7nm比较

Contacted Poly Pitch (CPP) (接触间距)

台积电和三星都为57纳米。

Metal 2 pitch (M2P)

三星是36nm,TSMC是40nm。

Tracks

三星最小单元Tracks高度为6.75,TSMC为6.0。

DDB / SDB

双扩散断路(DDB)或单扩散断路(SDB)。DDB在标准单元边缘需要额外的CPP宽度。TSMC光学工艺(7FF)是双扩散断路(DDB),而EUV工艺(7FFP)采用单扩散断路(SDB)。三星7nm EUV工艺采用的是DDB。

Transistor density(晶体管密度)

TSMC 7FF的最小单元逻辑密度为96.5 略好于三星 EUV 7LPP。而台积电EUV 7FFP则达到了113.9,比三星的EUV 7nm 7LP高出不少。

从图1来看,有趣的是,三星的7LPP工艺尽管使用了EUV和更小的M2P,但晶体管密度相比台积电的任何一个工艺都要低一些。此外台积电具有更小的轨道高度,对于没有EUV的台积电7FF,加入EUV后的7FFP可以减少掩模数,并增加SDB,使密度提高18%。

接下来看一下5nm的数据比较。

5nm

三星和台积电已经开始接受5nm的订单,今年的风险试产和明年的批量生产。我们预计两家公司将在5纳米采用更多的EUV层,三星为12层,台积电为14层。

三星表示他们的5nm工艺密度比7nm提高了25%,性能提升10%或功耗降低20%。据我们所知,三星的7LPP和5LPE之间的差异是6轨单元高度和SDB。这导致密度提高1.33倍。

这与台积电宣布密度提高1.8倍,性能提升15%或功耗降低30%形成鲜明对比。我们最近看到另一位分析师声称三星和台积电将在5纳米具有相似的密度,考虑到这两家公司具有类似的7纳米密度并且台积电宣布比三星更大的密度改进,我们相信台积电在5nm处将比三星具有显着的密度优势。

图2总结了使用与图1基本相同的比较指标。

图2. 5nm比较

从图2中可以看出,我们预计台积电的密度是三星的1.37倍,晶圆成本更低!

该表中另一个有趣的条目是TSMC达到30nm的M2P。据说台积电的目标是降低至28nm。台积电曾一度表示5nm的密度将提高1.9倍。

结论

我们相信,台积电的5nm制程在所有关键指标上都将显著优于三星的5nm制程,并将在明年投产时成为全球密度最高的逻辑制程。