像搭积木一样造芯片

2019-03-24 14:13:02 华夏幸福产业研究院

图片来源:英特尔

长期以来,我们看到的芯片通常是通过一套工艺在一个晶圆上完成的。以SoC(System on Chip)芯片为例,苹果最新手机使用的A12芯片集成了6核CPU、4核GPU、8核神经网络处理器,还有ISP、二级缓存、I/O等模块,整个芯片由台积电的7nm工艺制造而成。

那么,我们是否可能像搭积木一样,将不同工艺的芯片模块组装在一起来造芯片呢?这种芯片有哪些优势?该技术给芯片设计、工具、制造和封测带来哪些挑战?对未来产业有何影响?目前国内外企业又发展如何?本文依次给出答案。

“即插即用”的Chiplet模式

搭积木造芯片的模式名叫Chiplet(直译为小芯片),它是一类满足特定功能的die,我们称它为模块芯片。Chiplet模式是通过die-to-die内部互联技术将多个模块芯片与底层基础芯片封装在一起,构成多功能的异构System in Packages(SiPs)芯片的模式。

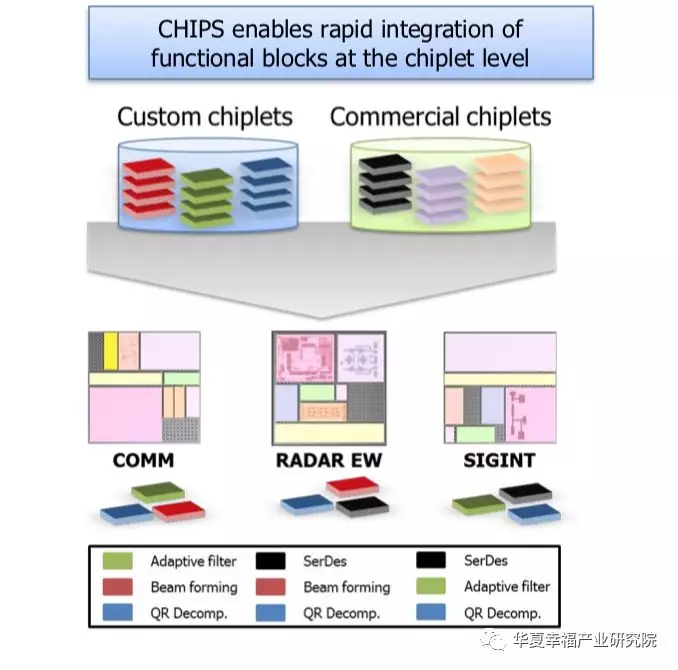

图1. DARPA关于Chiplet模式的愿景

图片来源:DARPA

Chiplet模式的玩家希望构建一个生态系统,这里有一个丰富的模块芯片库可供选择,集成商根据需求设计芯片架构,自由选择模块芯片交给制造商进行制造和封装。

与传统制造流程不同的是,集成商不再是购买IP,而是采购满足整体芯片架构的、即插即用的die,这样的die在工艺上不受其他模块的约束,工艺选择灵活,可以是逻辑的芯片,也可以是模拟芯片。

理论上讲,这种技术是一种短周期、低成本的集成第三方芯片(例如I/O、存储芯片、NPU等)的技术。

延续摩尔定律的新路径

Chiplet模式并不是新概念,上世纪八十年代工业界提出的multi-chip modules(MCMs)技术中就有涉及。在MCMs中,多个die被连接成模块,这些MCMs被用于大型机等高端系统中。

2017年,美国DARPA(Defense Advanced Research Projects Agency)再次将该技术引入大众视野。其在“电子复兴计划”中规划了名为“通用异构集成和IP重用战略”(Common Heterogeneous Integration and IP Reuse Strategies,CHIPS)的Chiplet项目,参与方包括英特尔、美光、Cadence、Synopsys多类型企业等。

Chiplet模式的再次受重视,源于被寄希望于解决当前芯片技术发展三个问题:

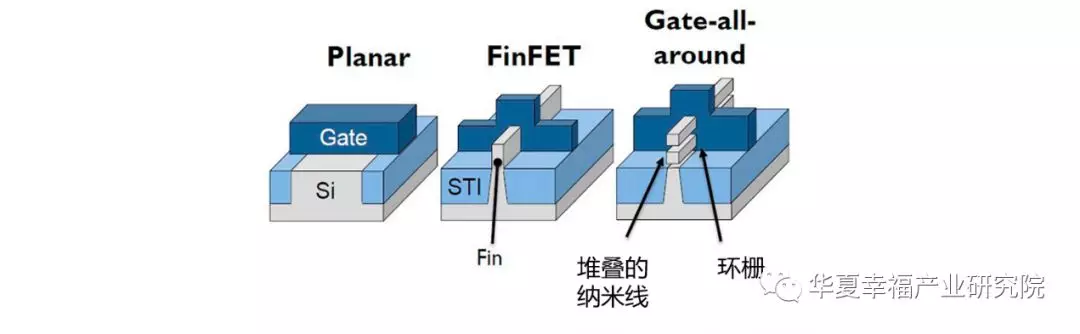

依赖器件尺寸缩减延续到摩尔定律难以为继。2018年,全球晶圆与联电相继退出7nm芯片制造战场。如今只有台积电和三星两家企业保持竞争。台积电2018年实现7nm量产,3nm预计2022-2023年量产。三星的7nm制程预计2019年底量产,3nm预计2021年量产。英特尔如今依然主打14nm工艺,10nm工艺2019年有望问世。在3nm环栅技术上,依赖尺寸缩减的摩尔定律可能将来到尽头。

图2. 先进工艺节点

图片来源:三星,华夏幸福产业研究院

先进制程芯片的设计成本大幅增加。芯片设计成本包括EDA软件、相关硬件、IP采购、芯片验证与流片和人力成本等。IBS数据显示,22nm制程之后每代技术设计成本增加均超过50%。设计一颗28nm芯片成本约为5000万美元,而7nm芯片则需要3亿美元,3nm的设计成本可能达到15亿美元。

图3. 先进制程下芯片设计成本大幅升级

数据来源:International Business Strategies,华夏幸福产业研究院

市场对高性能、多样化芯片有巨大需求。在未来社会智能化趋势下,大量模拟信号数据(图片、视频、声音、温度等)需要被高效的收集、处理,并作出决策。在当前AI算法框架下,一类场景即对应一类算法,也对应一类芯片(推理)。考虑芯片出货量难放量和高设计与流片成本问题,目前的芯片制造技术无法满足市场需求。

Chiplet技术有望在这样的背景下延续摩尔定律,以更快的速度、更低的成本,研制生产出更高性能的芯片产品,满足快速发展的智能经济、智能社会对新技术、新产品的需求。

Chiplet模式的优势

Chiplet模式的核心功能在于多功能模块的集成,技术优势主要是相对于SoC芯片和基于PCB板的集成技术,长期发展有望给现有半导体产业链和商业模式带来变革。其优势可总结为以下几个方面。

图4. Chiplet芯片相对单片SoC

和基于PCB的集成技术的优缺点

数据来源:Semico Research,华夏幸福产业研究院

功能模块选择更灵活。通过die-to-die连接技术,对连接到底层逻辑芯片的模块芯片原则上没有限制。例如各类AI加速模块、GPU、ISP、DSP、存储模块、I/O模块等。这些模块可以考虑特点,选择性价比最高的工艺节点进行制造,进一步提升Chiplet的灵活性。

拓展集成空间,提高集成度。Chiplet芯片一般采用3D集成方案,减小了芯片面积,扩展了空间。这有利于满足市场对AI芯片算力提升和成本降低的需求。

拓展系统优化空间。功能模块的3D互联给计算系统的架构设计既带来挑战,也带来更多优化空间。以AI芯片的应用为例,memory wall是核心瓶颈。对于云端AI加速场景,Host CPU和AI加速芯片的互联以及多片AI加速芯片间的互联,目前主要通过PCIe、NvLink或者直接用SerDes等。如果采用Chiplet技术实现片上互联,带宽、延时和功耗都会有巨大的改善。

催生新商业模式。若代工技术成熟,Chiplet可能在产业链中催生两种新角色,一种是Chiplet模块芯片供应商,一种是使用模块芯片的系统集成商。目前的AI芯片厂商,有的以供应IP或外接加速芯片为主,有的做集成AI加速功能的SoC芯片。对于前者,进化为Chiplet模块芯片供应商是个很好的选择。后者则可直接做模块芯片的系统集成商,这样能够极大缩短芯片开发时间。目前在IoT领域已有这样的供应商和集成商出现。

Chiplet模式给快速、低成本开发复杂功能的高性能芯片提供了一种可能。特别适用于中小企业开发应用于“小出货量场景”的芯片,也适用于一些“性能优先”的开发项目。

发展Chiplet的挑战

Chiplet模式的发展核心在于构建一个丰富的模块芯片库,使它们可以被自由选择,通过先进封装技术集成为复杂的异构系统。其发展目前主要面临四方面挑战。

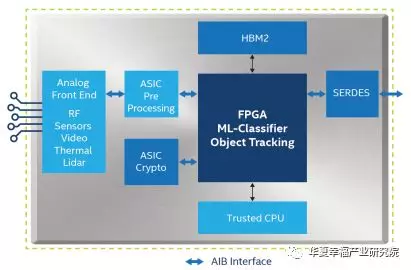

互联标准。首先,设计这样一个异构集成系统需要统一的标准,即die-to-die数据互联标准。为此,英特尔首先提出了高级接口总线(Advanced Interface Bus,AIB)标准。在DARPA的CHIPS项目中,英特尔将AIB标准开放给项目中的企业使用。AIB是一种时钟转发并行数据传输机制,类似于DDR DRAM接口。目前,英特尔免费提供AIB接口许可,以支持广泛的Chiplet生态系统,包括设计方法或服务供应商、代工厂、封装厂和系统供应商。此举将加速AIB标准的快速普及,有望在未来成为类似ARM的AMBA总线的业界标准。

图片来源:英特尔

封装技术。将多个模块芯片集成在一个SiP中需要高密度的内部互连线。可能的方案有硅interposers技术、硅桥技术和高密度Fan-Out技术,不论采取那种技术,互连线(微凸)尺寸都将变得更小,这要求互连线做到100%的无缺陷。因为互联缺陷可能导致整个SiP芯片不工作。

图6. 用于TSV互联的铜微凸点(micro bumps)显微图

图片来源:3DInCites

测试技术。作为一个复杂的异构集成系统,保证SiPs芯片功能正常比SoC更困难。SoC芯片通常需要采购IP,而目前关于IP的重用方法中,IP的测试和验证已经很成熟,可以保证IP接入系统没有问题。采用Chiplet模式的SiPs芯片则不同,它采购或使用的是制造好的die,即模块芯片。这对单个die的良率要求非常高,因为在SiPs中一个die的功能影响了整体性能,一旦出了问题损失巨大。同时在die设计中还需要植入满足SiPs芯片的测试协议。而对于SiPs芯片,由于管脚有限,如何单独测试每个die的性能和整体SiP的性能也是一个难点。

开发工具。上面提到的三个技术挑战,都需要软件工具的支持,对于EDA工具带来巨大的需求。例如在芯片设计中,30%-40%的成本是工具软件。DARPA的 CHIPS项目中一个工作重点就是设计工具。Chiplet技术需要EDA工具从架构探索,到芯片实现,甚至到物理设计提供全面支持。

产业机遇:Chiplet系统集成和模块芯片设计

从上面Chiplet模式发展的挑战看,产业机遇集中在芯片制造技术、封装测试技术和EDA工具技术。这些都是制造积木的手段,而设计什么样的积木和积木组合则有更加巨大的市场空间,即Chiplet系统集成和模块芯片设计。

产业发展早期,技术突破有望催生新增长点。如前文提到的封装与测试技术、EDA工具和互联标准都没有完善。此时以英特尔为代表的IDM企业有较大优势。IDM厂产业链完整的,研发投入大,可以集中突破封测技术和芯片设计。在DARPA的CHIPS项目中,也集中发展了EDA工具和集成标准,这无疑将加速产业成熟。

系统集成的市场空间更大。基于Chiplet模式的芯片在技术上优势明显,架构设计灵活,设计周期短,设计风险低,芯片集成度高,加工成本低。SoC芯片厂商有动力切入Chiplet芯片系统集成。此外,目前越来越多的制造业企业在自研芯片。Chiplet模式适用于小批量生产,开发成本低,研制周期短。对于新进入者,尤其是配套自用的企业,这无疑具有很大的吸引力。

垂直领域,模块芯片设计与系统集成可协同发展。随着垂直领域智能化需求的持续增加,针对某项应用的专用芯片与高性能逻辑芯片、存储芯片协同工作成为主流,这是Chiplet模式发展的基础。因而,传统专攻垂直领域计算芯片厂商转行开发Chiplet芯片有着巨大优势。

AI芯片适用于Chiplet模式。在现有算法框架下,AI芯片就是一类专用芯片,在Chiplet模式下,与逻辑、存储芯片共存是非常适于AI芯片的工作方式。例如目前新兴的存内计算和光子计算(模拟计算方案),这些芯片的制备通常在较低的工艺节点上,与提倡高集成度的逻辑和存储芯片集成成为难点,采用Chiplet模式则对工艺节点则没有要求。

头部企业发展现状

目前,Chiplet模式还处于发展早期,主要围绕DARPA的CHIPS项目发展。在CHIPS项目中,有制造封测企业如英特尔、Northrop、Micorss等,还有模块芯片开发企业和高校如Ferric、Jariet、镁光、Synopsys和密西根大学,以及EDA工具开发企业和高校如Candence和佐治亚理工。

下面,我们介绍IDM大厂英特尔和一家中资企业极戈科技的发展。前者有先进的封装技术和集成标准,后者采用Chiplet模式极大地缩短了物联网芯片的研发周期。

01. IDM厂:Intel,3D封装技术和AIB集成标准

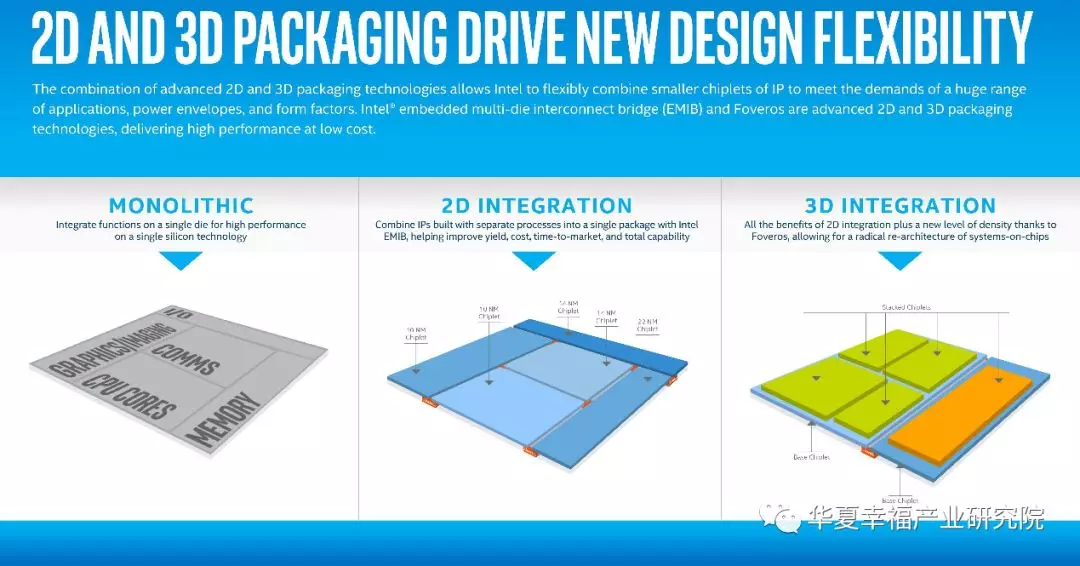

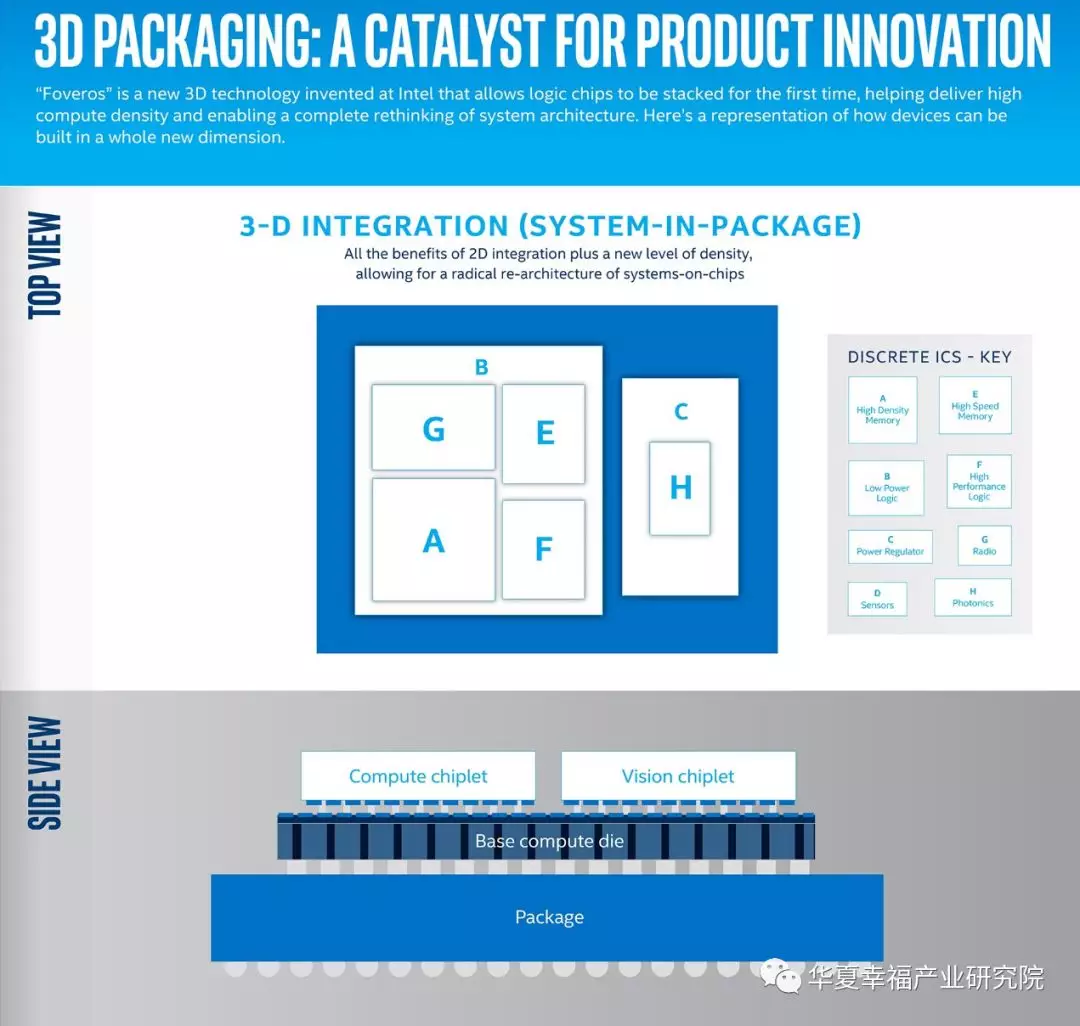

英特尔是国际芯片设计、制造和封测的领先企业,拥有完整的产业链和超高的研发实力。它们将Chiplet模式当作延续摩尔定律的首要手段。2018年12月,英特尔推出了业界首个3D逻辑芯片集成技术——Foveros。

图片来源:英特尔

该技术整合了其早前提出的2D封装技术——嵌入式多裸晶互联桥,可以将多个IP的模块芯片灵活组合。例如I/O、SRAM等电路对先进制程没有要求,可以用低制程加工在基础芯片上。而逻辑芯片、GPU等逻辑电路,先进制程可以提供更好的性能和更低的功耗,可以加工成模块芯片,堆叠在基础芯片上。

图8. 英特尔 3D封装技术示意图

图片来源:英特尔

Foveros结合EMIB可以满足各种不同应用、功率范围和外形尺寸的需求,提供低成本、高性能芯片选择。英特尔预计将于2019年下半年推出一系列采用Foveros技术的产品。首款Foveros产品将整合高性能10nm模块芯片和低功耗的22nm基础晶片。

英特尔还是DARPA CHIPS项目的主要参与者之一,其免费提供AIB接口许可,这将有利于催生更多的Chiplet和系统集成企业。

02.系统集成企业:极戈科技

极戈科技(zGlue)2014年成立于美国硅谷,2017年进入中国。创始人张铭毕业于北京大学,在UIUC获得硕士与博士学位。曾在英特尔和三星工作。

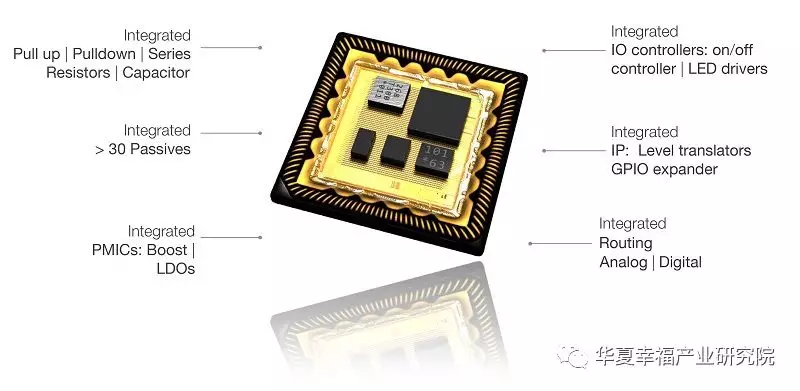

极戈科技主打快速芯片设计和制造,通过独特的电路设计+封装+ SDK+算法,能够将物联网芯片的设计制造流程从超过1年压缩到2-4周。

极戈科技利用SaaS的模式提供芯片设计方案,也采用2.5D/3D封装技术。基础芯片是极戈开发的硅基芯片,上层是第三方的模块芯片,包括传感器、通讯、存储等,从而低成本、高速度地实现小体积,低功耗的系统集成。

图9. 来自极戈的ZiP芯片

图片来源:极戈科技

目前,极戈的产品主要用于蓝牙、NB-IoT、WiFi和可穿戴产品中,有超过100款模块化芯片产品可供选择。

2019年1月底,极戈科技携手台积电和日月光,推出业界首个3D IC定制服务——快速制造项目。据称,该计划可以将一年的设计和生产时间缩短到一个月,把几百万美元的开发成本降低至几千美元。

图10. 极戈科技的ZiP集成平台的技术优势

图片来源:极戈科技

结语

Chiplet模式的发展还有很长的路要走,它既是一次技术升级,包括封装测试技术、EDA工具、芯片架构设计等,也可能带来一次对传统半导体产业链的重构。我们有理由相信,随着越来越多的企业进入,Chiplet系统集成和模块芯片设计行业将会得到快速发展,受益于时间和成本,AI、AIoT等智能产业的发展进程也将加速。

参考资料:

1. 美国DARPA项目:Common Heterogeneous Integration and IP Reuse Strategies(CHIPS)

3. MARK LAPEDUS:The Chiplet Race Begins