芯片设计中电迁移和IR压降的挑战和技术

2019-03-24 14:11:27 EETOP在本文中,我们将讨论电迁移和IR下降的问题,以及防止这些问题在电子设备中发生的技术。

紧凑型电子设备的技术趋势和需求要求采用现代集成电路设计。电子设备制造商正在成倍地降低金属互连线的宽度。因此,互连线的横截面积正在减小。此外,由于功能集成和设备互连的不断增加,芯片上会有更多的连线。因此,,在小于16nm的节点上工作的任何器件在一段时间内容易受到性能问题的影响,这是由于不能通过成比例的电流,导致电迁移和IR下降的问题。

什么是电迁移?

电迁移(EM)是一种分子位移,是由于导电电子和离子在一段时间内的动量转移而引起的。当电流密度较高时会发生这种现象,这会导致金属离子向电子流方向漂移。EM通常发生在现场设备部署多年之后。

由于电迁移效应,金属线可能会爆裂并短路。EM会增加导线电阻,这会导致电压下降,从而导致设备降速。由于短路或开路,它还可能导致电路永久性故障。EM进入带温度的正反馈回路(焦耳加热)。下面是如何用布莱克方程(Black’s Equation)求金属线的平均失效时间(MTTF)。

导线的电迁移可靠性:

A =横截面积依赖常数

Jn =电流密度

E a =活化能(Activation energy )

k =玻尔兹曼常数

T =开尔文温度

N =比例因子(通常根据黑色设置为2)

什么是IR Drop?

IR压降是指出现在集成电路中电源和地网络上电压下降或升高的一种现象。随着半导体工艺的演进金属互连线的宽度越来越窄,导致它的电阻值上升,所以在整个芯片范围内将存在一定的IR压降。IR压降的大小决定于从电源PAD到所计算的逻辑门单元之间的等效电阻的大小SoC设计中的每一个逻辑门单元的电流都会对设计中的其它逻辑门单元造成不同程度的IR压降。如果连接到金属连线上的逻辑门单元同时有翻转动作,那么因此而导致的IR压降将会很大。然而,设计中的某些部分的同时翻转又是非常重要的,例如时钟网络和它所驱动的寄存器,在一个同步设计中它们必须同时翻转。因此,一定程度的IR压降是不可避免的。IR压降有静态压降和动态压降两种类型。

静态IR压降:

静态IR压降是设计的平均压降。它取决于将电源连接到相应标准单元的电源网络的RC。平均电流完全取决于时间段。栅极沟道漏电流是静态IR压降的主要原因。

Vstatic_drop = Iavg x Rwire

动态IR压降:

动态IR压降是由于晶体管的高频开关通断而引起的电压下降。当由于芯片的开关活动而对来自电源的电流的需求增加时,会发生这种情况。动态IR压降依赖于逻辑的切换时间,对时钟周期的依赖性较小。动态IR压降是对大量电路开关同时产生的IR压降引起的峰值电流需求进行评估。当前的需求可能是高度本地化的,并且可能在单个时钟周期(几百ps)内很短,并且可能导致IR压降,从而导致额外的建立和保持时间无法满足。通常,时钟网络上的高IR压降会导致时钟保持时间不够,而数据路径信号网络上的IR 压降会导致设置时间不够。在这种情况下,您可以将标准单元分离开来,这样就可以减轻为满足许多标准单元而产生的负载。

Vdynamic_drop = L(di / dt)

一个例子:

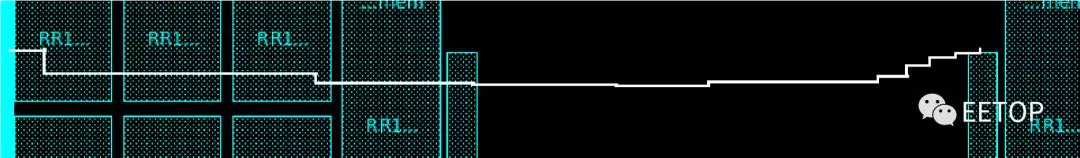

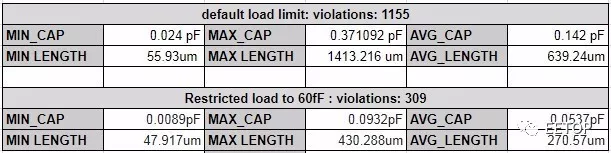

我们在信号/时钟网上观察到1155次电迁移违规。我们的max_cap为371fF负载,平均净长度为~640um。电容负载基于标准单元库中的默认值。这使得网络允许更多电流。

APSDRC_net_210033的总电容:0.34327 APSDRC_net_210033的总长度:1345.995

我们看到时钟单元周围的IR压降,因为它们总是以50%的占空比进行切换。我们观察到在时钟单元附近存在标准单元,整个区域通过该单元变得非常密集。因此,这些区域周围出现了IR压降。

除了时钟,我们还在一些耗电量大、密度高的单元上发现了IR压降点。

防止电迁移和IR压降的技术

电迁移缓解

1. 对EM违规网络应用NDR(非默认规则)

获得EM结果后,您可以获取净形状并使用NDR重新路由这些网络。应用NDR涉及使用具有更大间距的双宽或三宽金属来布线时钟网络。这将快速消除大多数EM违规行为,甚至可以预测网络,这些网络更可能基于两个参数进行EM违规:

1)驱动强度

2)负载。

可以过滤掉更多负载和高驱动的网络,并将它们移动到NDR。可以根据项目统计数据决定不同驱动强度的阈值负载。

示例:我们看到其中一个单元出现了惊人的改进

Command: create_routing_rule em_ndr -widths“M2 0.064 M3 0.064 M4 0.064”-cuts {{VIA1 {Vrh 1} {Vrv

1}} {VIA2 {Vrh 1} {Vrv 1}} {VIA3 {Vrh 1} {Vrv 1}} {VIA4 {Vr 1}}}

foreach net [gon [get_nets $ nets]] {set_routing_rule $ net -rule em_ndr}

这些设置之前,有309次违规,在应用NDR后减少为1次。

2. 限制网络的负载目标

限制或减少负载也可有助于防止电迁移的发生。在上面的例子中,我们看到142fF是设计中的平均电容。根据一些实验的统计数据,我们限制所有网络的最大负载为60fF。结果,我们看到信号EM和平均净长度都有很好的改善。

Command:set_max_capacitance 0.06 [current_design] #setting max_cap_value用于设计

缓解 IR 压降

1. Padding clock cells

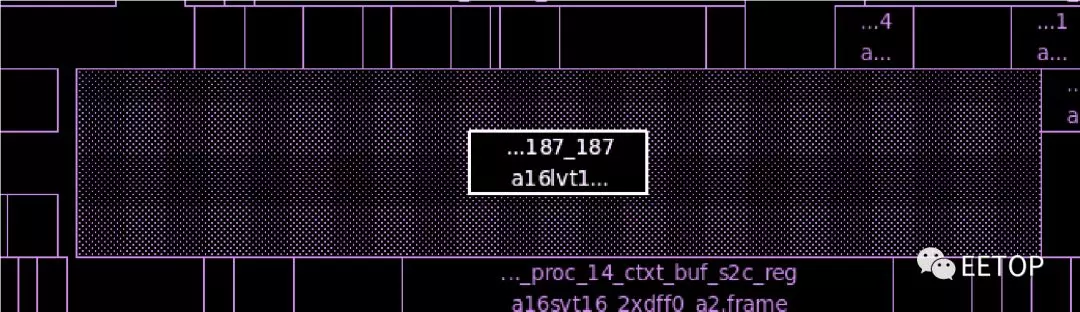

当涉及到IR时钟问题时,由于高时钟切换,时钟结构是芯片功耗的主要原因。然而,利用 Padding clock cells 技术,时钟缓冲器/反相器和时钟门单元被赋予额外的区域作为禁止布线区,以避免标准单元的放置和它们周围任何过量的单元密度。这有助于防止动态IR压降。

Command: create_keepout_margin -outer {3.6 0.576 3.6 0.576} $clock_type_keepout IMAGE: A cell with cell padding

2. Cell Padding/Decap insertion around cells within a dynamic IR hotspot region

一些驱动强度高的单元会产生动态IR压降问题。可以为这些单元提供单元衬垫,或者在其周围或IR压降区域插入decap单元格,以防止IR 压降问题。