全球顶尖芯片专家揭秘【低功耗芯片设计】真相

2019-01-08 12:39:52 清谷资本作者:新帆人(清谷资本)

摘要

低功耗芯片设计是本世纪以来最重要的新兴设计方法。可以说没有低功耗设计,就没有今天的智能手机,移动设备,物联网,及高性能计算等产业。本文从芯片功耗和电源噪声的分析开始,介绍了低功耗设计的几种常用方法,并给出了低功耗设计的几种可能的发展方向。可以预见,作为一种最新的芯片设计方法,随着芯片图形尺寸越来越小,低功耗设计在现在及未来的芯片中会起到越来越重要的作用。

——新帆人

回顾芯片设计的发展,我们看到大致可以分为三个阶段:

第一个为解决设计复杂度的阶段:80年代开发的逻辑综合工具极大得提高了设计效率及规模;第二个为提高时钟频率的阶段:90年代为了提高运算速度,时钟频率从几十MHz提高到几百MHz,甚至达到了GHz。(例如本世纪初Digital公司的Alpha芯片的时钟频率为1.4GHz)。芯片设计也是围绕着时钟频率与时序进行,例如像时序驱动的逻辑综合及布局布线等。第三个为低功耗设计阶段。我们知道,CMOS电路(绝大多数集成电路芯片都采用CMOS电路)的动态功耗(也叫工作功耗)与时钟频率成正比,同时也与电源电压的平方成正比。这样一来,随着时钟频率的增加,芯片的功耗也随之快速上升(例如Alpha芯片的功耗为125瓦)。进入二十一世纪后,人们逐渐认识到单纯靠增加时钟频率再也不能提高性能了。相反的,功耗的增加带来了一系列问题。例如芯片温度增高引起的散热及电路性能下降,电源及信号噪声管理(power integrity - PI, signal integrity - SI)等。本世纪初以来移动设备特别是手机的兴起更是引发了低功耗芯片设计的浪潮。

英特尔曾在1999年给出了其处理器功率密度随着时间的变化(如图1所示)。可以看到,按照当时的发展趋势(摩尔定律),晶体管的尺寸逐年缩小,芯片上的功率密度将很快达到甚至超过核反应堆甚至火箭喷口的功率密度 --- 这是一个不可控的状态。因此,当时的业界共识是35纳米就是工艺水平及其电路的极限了。

然而事实上,现在的工艺水平已经达到了7纳米,而且还在继续往前发展。这里面低功耗设计功不可没。可以说没有低功耗设计,就没有纳米级的电路及芯片,更不用说我们人人使用的智能手机了。

下面我们简单介绍一下芯片上的电源网络以及低功耗设计常用的方法。

我们知道,芯片功耗主要由三部分组成:动态功耗(也叫开关功耗),短路功耗,及静态功耗(也叫泄漏功耗)。其中动态功耗是逻辑门在工作时给负载电容充放电引起的,短路功耗是逻辑电路翻转过程中造成瞬态短路引起的,而静态功耗是由于逻辑电路中的泄漏电流引起的。因此,低功耗设计主要是围绕着如何减少这三部分功耗来进行的。

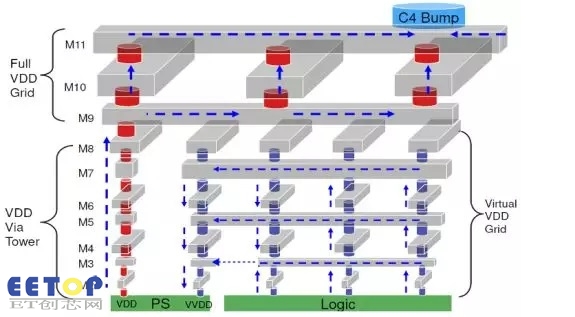

平时我们看到的电路图里面的电源线(及地线)都是一根细细的导线。实际上,芯片里面的电源网络十分复杂。图2给出了一个典型的芯片电源网络。可以看到,从最上面的封装接触点(C4)到最下面的晶体管电路(Logic),导线多达十几到几十层。每两层导线中间有通孔(Via)连接。从上至下,导线由宽到窄,由厚到薄。这些导线形成一个庞大的由寄生电阻电容组成的网络(如果工作频率很高,还要加上寄生电感)。如今的一个系统集成(SoC)芯片里,电源网络里的节点数以及寄生器件可达数十亿之多。

我们可以把芯片上的电源网络比喻成一个庞大的输水灌溉系统:电源就是水库,电源导线就是水渠,而晶体管则是地里的庄稼。水渠起到的作用就是把水从水库输送到田里的庄稼。引水的水渠也是由宽到窄,由深到浅,最终将水引导并浇灌到每一颗庄稼上。

电源噪声及其影响

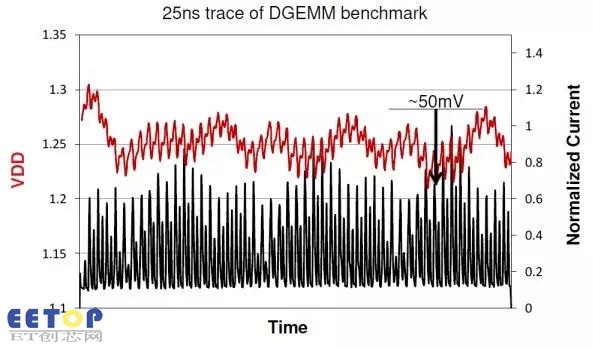

最初人们在设计电路时,总是假定电源电压是个恒定值。实际上,电源网络上的电压并不是恒定的设计值,而是随着电路的工作上下起伏。这是因为电源网络上有很多的寄生电阻和电容(如果工作频率足够高的话还要考虑寄生电感)。如果电源网络设计得不好,就会造成电压起伏过大,从而导致电路性能下降,甚至不工作。图3给出了芯片电源上的电源电压及电流。可以看到,在短短的几纳秒内,电源电压的变化就达到50毫伏。

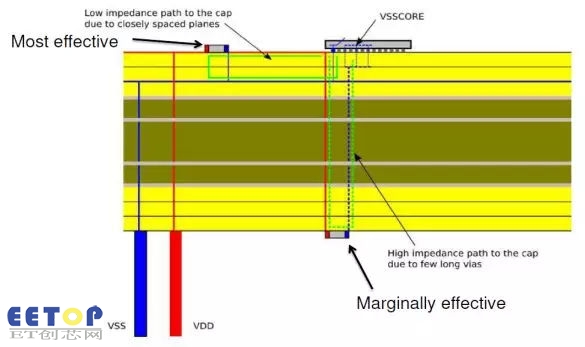

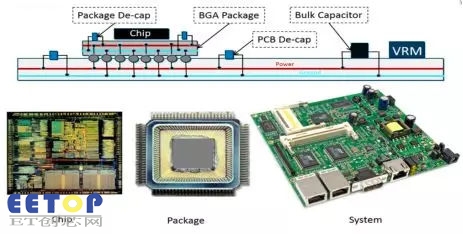

一种有效减少电源电压噪声的方法是在电源网络上加去耦合电容(decoupling capacitor)。去耦合电容就像安放在水渠旁防旱涝的蓄水池:当水位过高时,可以往蓄水池里放水以防止水位高过河床。当水位过低时,可以把蓄水池里的水放到水渠里,以保证水渠里的水位稳定。同样的,去耦合电容也起到稳定电源电压的作用。去耦合电容可以分成几类:芯片级,它们的电容值最小,在fF(1E-15F)范围;封装级,它们的电容值居中,在pF范围(1E-12F);以及电路板级,它们的电容值最大,在nF-uF范围(1E-9F到1E-6F)。可以看到,它们的电容量有数量级的差别,分别用来过滤不同频段的噪声(100MHz-1GHz, 10MHz-100MHz, 100KHz-10MHz)。值得注意的是芯片上的元器件也会对去耦合电容有所贡献(例如晶体管上的寄生电容,以及导线之间的耦合电容)。如何摆放去耦合电容是个十分复杂的问题。如果去耦合电容离工作单元摆得过远,则起不到减少电压噪声的作用。就像蓄水池如果离水渠过远,就无法及时调节水位。图4给出了电路板上的两个去耦合电容的例子。可以看到,由于上面的去耦合电容离芯片近,其所起的作用就远远好过下面的去耦合电容。

图4:电路板(PCB)上的去耦合电容

为了保证电源电压噪声不影响电路的正常工作,就需要对整个芯片进行电压噪声分析。电压噪声分析可以帮助设计者发现电源网络中的薄弱环节,以及芯片上的“热点”(hot-spot),即芯片上功耗和电源噪声最大的地方,以便加以改进。电压噪声分析的方法分为静态和动态两种。静态方法是在上个世纪90年代后期开发的。它的基本思想很简单,就是把电源网络看成一个庞大的电阻网络,把电路里的每个逻辑门看成一个直流电流源,然后来解欧姆定律:(1/R)V=I。注意这是在求解全芯片的欧姆定律,网络里包含从数百万到数十亿个电阻,以及数百万到数亿个电流源,非常具有挑战性。然而把芯片工作状态当成直流的欧姆定律来解也有很多局限。最明显的就是CMOS是动态工作的电路,把一个真实的瞬态电流及电压波形用一个固定的直流值来代替,会损失很多精度。

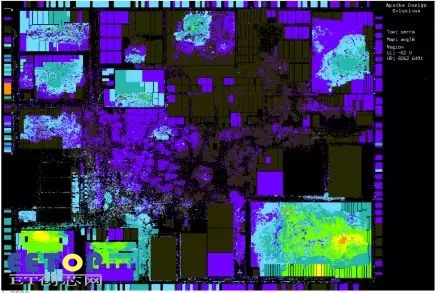

到了本世纪初,人们意识到以上静态分析方法的局限,因此开发了用真实的瞬态电流波形来做动态模型与分析。这个难度比静态分析还要大一个数量级。首先电源网络上除了寄生电阻之外,还要考虑寄生电容以及去耦合电容。如果工作频率很高,或者分析中包含芯片封装的话,还要考虑寄生电感效应。其次要进行时域的瞬态分析。因此在高性能的服务器上跑一个瞬态分析下来要用2-3天的时间。动态分析的优点是它的高精确度,它的结果更接近真实物理状况(例如可以看到去耦合电容效应),是芯片设计里不可或缺的分析工具(sign-off analysis tool)。图5给出了一个全芯片的动态压降分布图。

图5:全芯片的动态压降图

在以往的设计过程中,芯片,封装,和系统都是分开进行的。自从有了以上的功耗分析工具后,设计者就可以进行整体的分析及优化。例如,以前封装的设计者没有芯片精确的功耗模型,只好要么用粗略的估算,要么留出过多的余量。而现在有了芯片功耗分析工具之后,就可以产生精确的芯片功耗模型(Chip Power Model – CPM),使得芯片-封装-系统的整体优化成为可能。图6给出了芯片-封装-系统的整体优化的示意图。

低功耗电路设计方法

上面讲到了功耗以及它带来的电源噪声。为了减少功耗及其影响,过去十多年来发展了很多低功耗设计方法。例如,既然动态功耗与电压的平方成正比,我们可以对芯片内部的电路使用低电压(比如1.0V),而芯片上对外接口的驱动电路使用高电压(比如3.3V),这就是所谓的多域电源设计 (Multi-power domain)。对芯片内部的电路还可以再细分,比如对需要高速运算的电路(像时钟驱动电路)采用低阈值的逻辑单元,虽然它的泄漏电流要大一些,但可以满足短延迟的要求。对一般的逻辑电路可以采用高阈值的逻辑单元以减少泄漏电流。这就是所谓的多阈值逻辑单元设计 (Multi-Vt CMOS)。时钟电路的动态功耗通常要占到芯片总体动态功耗的30-40%甚至更多,因此芯片设计者们也把时钟分成了许多域(Multi-clock domain),有的芯片上时钟域甚至达到了数百个之多。

下面我们就来介绍几个典型的低功耗设计与管理方法。

低压降稳压器(Low Drop-Out regulator - LDO)

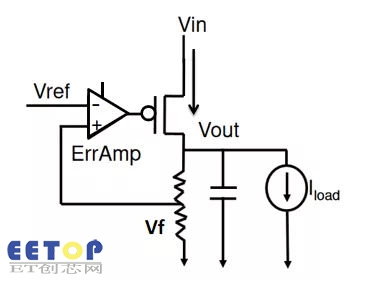

低压降稳压器是一种直流线性稳压器,其电路由PMOS传输门,高增益误差放大器,及分压电阻组成(有时也带有去耦合电容)。它可以提供大范围的电源电压输出,具有噪声小,低成本,集成度高的优点,因此在低功耗设计中广泛使用。

图7:低压降线性稳压器

低压降稳压器的工作原理是利用反馈来进行稳压的。从图7可以看到,PMOS传输门的输出端(漏极),亦即LDO的输出端通过分压电阻接到了增益放大器的输入端,而增益放大器的输出端又接到了PMOS传输门的输入端(栅极)。因此,LDO输出的电流和电压将会受到传输门的控制。其反馈工作原理如下:Iload 增大,Vout 下降,导致Vf 下降,Vin=Vf – Vref 下降,PMOS的栅压Vgate 下降,Vgs = Vin – Vgate 增大,Ipmos( Iload )增大,Vout下降减小,因而达到稳压的目的。

当然,真正芯片上的LDO电路会比上面的原理图复杂很多。例如采用多级的误差放大器,PMOS传输门阵列等等。但基本原理是一样的。

动态压频调节

(Dynamic Voltage Frequency Scaling - DVFS)

动态压频调节主要针对的是减少动态功耗。我们知道,动态功耗和电路工作频率成正比,也和电源电压的平方成正比。因此,如果能随时判断出电路的工作状态,并随之调整工作频率及电源,就可以达到减少功耗的目的。

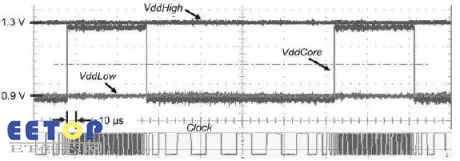

图8:具有两个电压值(VddHigh, VDDLow)的动态压频调节原理图

图8给出了一种动态压频调节的实现原理图。首先,提供了两个电源电压VDDHigh和VDDLow,电压控制的震荡器(VCO),以及动态压频调节控制器(DVFS Controller)。

动态压频调节控制器会根据电路的工作状态来决定电源电压和工作频率。例如,当执行一个访问存储器的指令时,需要好几个时钟周期,这时就可以降低运算逻辑电路的电源电压及工作频率,等下一组数据传回来后,再把运算逻辑电路的电源电压及工作频率恢复回来,以便满足性能的要求。图9给出了处理器内核的电源电压(VddCore)随着工作状态在两个电源电压(VddHigh=1.3V, VddLow=0.9V)之间变化的波形。同时还给出了时钟变化的波形。可以看到,当电源电压为VddLow时,时钟频率也随之降低了。

图9:具有两个电压值(VddHigh, VDDLow)的动态压频调节波形图

动态压频调节是为了减少芯片工作时的功耗,因此设计者需要十分了解芯片上各个模块的工作状态,才能设计出好的动态压频调节控制器,同时在时序优化上也要考虑到电压的变化。一个好的动态压频调节可以做到节省20%的动态功耗。

电源阀门(Power Gating)

电源阀门主要针对的是静态功耗(泄漏电流引起的功耗)。其基本思想就是在某些功能模块不工作时,把它的电源断开。这是因为在晶体管的亚阈值范围内,泄漏电流与电压是呈指数的关系,因此这种方法对减小静态功耗效果十分显著。图10给出了电源阀门的示意图。其中的开关是用MOSFET晶体管做的。这个开关把电源分成了两个区域:连接电源的一边叫真实电源域(VDD domain),连接电路的一边叫虚拟电源域(Virtual VDD domain)。真实电源域的电压值是不变的,而虚拟电源域的电压值是根据电源阀门的状态改变的。当电源阀门闭合时(ON),虚拟电源域的电压值十分接近VDD(VDD减去电源阀门上的压降);而当电源阀门断开时 (OFF),虚拟电源域的电压值十分接近0(电源阀门的漏电流与电路静态电阻的乘积)。

除了把电源阀门放在VDD上,也可以把电源阀门放在VSS上。其相对应的叫虚拟VSS域(Virtual VSS domain)。VDD上的电源阀门叫头开关(header switch),而VSS上的电源阀门叫脚开关(footer switch)。

图10:电源阀门示意图

从上面我们可以看到,要实现一个理想的电源阀门,会对这个小小的开关有很多要求:导通时的电阻值要小;断开时电阻值要很大(以减小其漏电流);开启和断开的响应要快。实际上,芯片里的电源阀门不只是单独一个晶体管开关,而是由成百上千个晶体管开关组成的。如何摆放这成百上千个电源阀门,需要进行准确的计算和分析。图11给出了一个电源阀门在芯片上的布局。每一个红点代表一个电源阀门开关。可以看到,很多电源阀门分布在各个功能模块的电路周围,在静态存储器周围也布有电源阀门。

在设计电源阀门时,一个很重要的步骤就是分析其开启过程。电源阀门的开启过程就像水库开闸放水一样。一方面希望尽量在短时间内完成,但另一方面又要可控,使得涌流不能太大(in rush current)。如果涌流太大,就会影响到旁边的电路模块的电压稳定,也会产生电源线/地线上的噪声。长期多次的大涌流会造成电子飘移 (EM – Electron Migration),使得导线断开或短路,就像水库开闸放水,如果水流过大,就有可能冲开河堤一样。因此,这些电源阀门并不是同时开启的,而是按照一定的顺序和时间依次打开的。这样就可以有效地控制涌流。

图12给出了一个使用脚开关的开启分析结果。可以看到,在100ns期间,VSS(粉色曲线)从3V降到0V,而电流(蓝色曲线)在10ns时达到了近3A的峰值。

图12:电源阀门(脚开关)开启时的电压VSS与电流I(VSS)随时间的变化

结语

如我们之前所说,功耗已经成为目前芯片设计中最重要的因素。

1)功耗会影响电路性能,芯片散热,以及芯片可靠性等一系列问题;

2)芯片的功能及时序设计与优化已相对成熟,但功耗上的优化还有很多文章可做;

3)电源电池容量的增加相对有限,而且受到安全因素的限制(例如前些时候发生的三星手机电池爆炸)。

以上我们介绍了在电路级上进行低功耗设计及优化。实际上,人们也在探索在其它设计层次上的低功耗设计及优化。例如,现在已经开发出了寄存器传输级(RTL)上的功耗估算及优化。架构级( architecture)上的功耗估算及优化也在研发中。这是由于越早在设计周期中及越高层次的设计中考虑功耗,就会得到越大的回报。除了在硬件上进行功耗优化,人们也在从软件角度来进行降低功耗的努力。最明显的例子就是操作系统级里的电源管理,把不在运行的程序和App放置在休眠状态(sleep mode)。除此之外,人们也在探索在编译器里加入功耗优化的功能,使得程序和App在运行中也可以达到功耗最低。可以预见,随着器件工艺,电路设计,系统集成,和软件开发的不断完善,低功耗设计也会在以上的各个方面不断发展进步。