Altera启动嵌入式计划

2010-10-16 15:38:02 本站原创Altera引用Intel有关“培育黑天鹅(指不可测的重大事件)”的描述,认为未来填补工艺效率的功耗瓶颈的方法正是体系结构的创新,而IBM在有关服务器产品的白皮书中也认为在系统开发后期,提供FPGA辅助芯片非常有利于增加新固件,增强卸载功能。IBM希望这一基于硬件的新解决方案能够成为未来设计的基础。

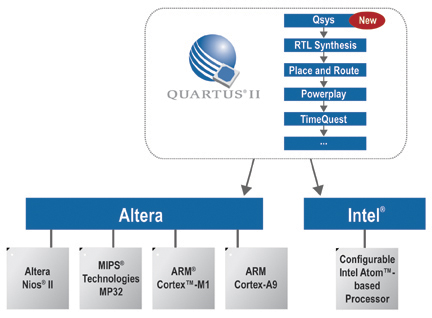

有鉴于此,Altera正式启动了嵌入式计划,该计划提供了基于Quartus II开发软件的单一FPGA设计流程——包括新的Qsys系统级集成工具、公用FPGA知识产权(IP)库,以及新的ARMCortex-A9 MPCore和MIPS技术公司MIPS32嵌入式处理器产品等。

罗嘉鸾介绍,Qsys系统级集成工具可以使嵌入式设计人员面向Altera Nios II、基于ARM和MIPS的嵌入式处理器以及最近发布的可配置Intel Atom处理器开始设计。Qsys利用了业界首创的FPGA优化芯片网络技术来支持多种业界标准IP协议,提高了结果质量,具有很高的效能。Qsys采用SOPC Builder界面,支持与现有嵌入式系统移植的后向兼容。而且,这一高级互联技术将支持分层设计、渐进式编译以及部分重新配置方法。“Qsys是Altera SOPC Builder工具的后续产品,引入了FPGA优化芯片网络技术,与SOPC Builder相比,存储器映射和数据通路互联性能提高至两倍,”罗嘉鸾说,“SOPC Builder适合单层次设计,而Qsys提高了系统级设计效能,适合多层次设计,并且,Qsys支持业界标准IP接口,如AMBA,使之可以支持设计重用。”

罗嘉鸾介绍,Qsys系统级集成工具可以使嵌入式设计人员面向Altera Nios II、基于ARM和MIPS的嵌入式处理器以及最近发布的可配置Intel Atom处理器开始设计。Qsys利用了业界首创的FPGA优化芯片网络技术来支持多种业界标准IP协议,提高了结果质量,具有很高的效能。Qsys采用SOPC Builder界面,支持与现有嵌入式系统移植的后向兼容。而且,这一高级互联技术将支持分层设计、渐进式编译以及部分重新配置方法。“Qsys是Altera SOPC Builder工具的后续产品,引入了FPGA优化芯片网络技术,与SOPC Builder相比,存储器映射和数据通路互联性能提高至两倍,”罗嘉鸾说,“SOPC Builder适合单层次设计,而Qsys提高了系统级设计效能,适合多层次设计,并且,Qsys支持业界标准IP接口,如AMBA,使之可以支持设计重用。”

作为该计划的一部分,Altera将继续拓展目前的嵌入式合作伙伴计划,联合ARM、Intel和MIPS技术公司以及FPGA业界的多个合作伙伴。此外,Altera将与他们协作,增强设计流程,支持越来越多的FPGA嵌入式处理产品走向市场。这些合作已陆续体现在产品中,例如Intel即将推出的基于Atom的可配置新处理器就在多芯片封装中采用了Intel Atom E600系列以及配对的Altera FPGA。对于希望采用专用I/O或者加速硬件的用户而言,新架构提高了他们的灵活性。

Altera上半年已与ARM签署了协议,授权包括Cortex-A9

Altera还进一步扩展了软核处理器,将在2011年上半年推出基于MIPS技术公司MIPS32处理器体系结构的MP32软核处理器。MP32是Altera、MIPS技术公司以及主要用户过去几年密切协作的结果。它针对Altera器件完善了Altera Nios II嵌入式处理器以及合作伙伴软核CPU系列产品,极大的丰富了FPGA可以使用的操作系统和应用程序。

罗嘉鸾最后表示,Altera将在本季度末发布有关Qsys和嵌入式计划更详细的信息。

EETOP 官方微信

创芯大讲堂 在线教育

创芯老字号 半导体快讯

相关文章

0

0