欧洲本土超级计算硬件迈出第一步!高性能计算RISC-V完成流片,样品测试"Hello World "成功显示!

2021-09-23 13:03:49 EETOP最新消息,专为高效率和高吞吐量计算设计的被称为欧洲处理器加速器(EPAC)芯片已成功流片,并正在EPI的实验室进行测试。EPI认为这标志着向本土超级计算硬件迈出的第一步。

欧洲处理器计划最初是一个由来自 10 个欧洲国家的 28 个合作伙伴组成的项目,旨在为欧盟配备定制处理器和技术,使欧盟成为专注于科学和创新的技术独立力量。为实现这一目标,该项目旨在构建一个完全定制的 HPC 系统,从定制处理器开始。正如该项目所指出的:“EPI 活动的一个关键部分是基于 RISC-V 指令集架构开发和展示完全由欧洲开发的处理器 IP,提供名为 EPAC(欧洲处理器加速器)的高能效和高吞吐量加速器内核.”

今天,随着第一批芯片在EPI的实验室中测试,该项目已经兑现了承诺。RISC-V 处理器是包含多个专用加速器的设计,所有加速器都以 RSIC-V ISA 及其设计原则为中心。该处理器包含四块矢量处理单元(VPU),由 SemiDynamics 设计的 Avispado RISC-V 内核和巴塞罗那超级计算中心和萨格勒布大学设计的矢量处理单元组成。在每个tile中,都有用于缓存系统的主节点和 L2 缓存,这是 Chalmers 和 FORTH 的贡献。对于额外的加速,有由Fraunhofer IIS、ITWM 和 ETH Zürich 设计的 Stencil 和 Tensor 加速器 (STX),以及由 CEA LIST 设计的精度可调处理器 (VRP)。

为了保持所有这些组件之间的连接,EXTOLL开发了一个高速的片上网络(NoC)路由器和SERDES。到目前为止还不知道其他的芯片外连接,但是,我们假设将利用DDR5和PCIe Gen4或Gen5 I/O。

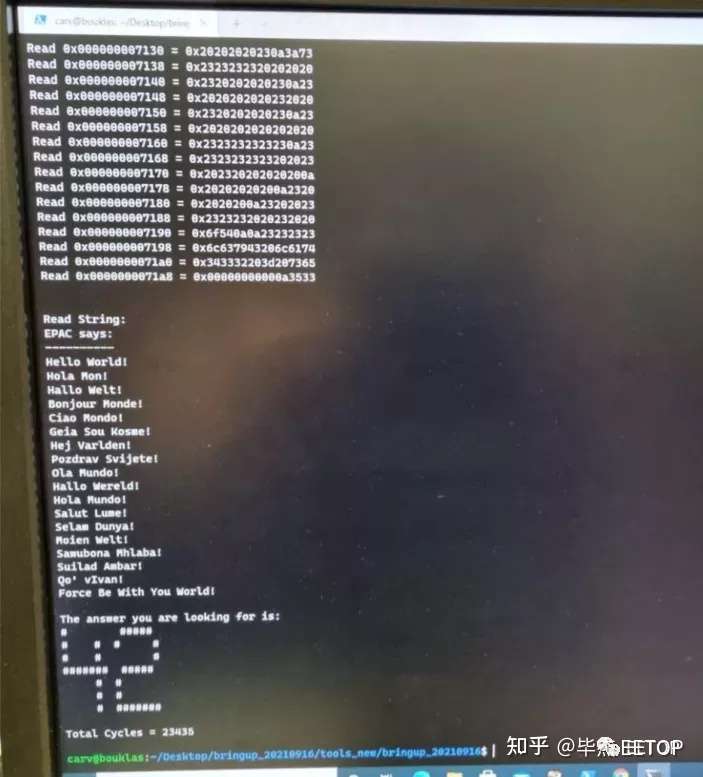

该芯片已经在GlobalFoundries 22纳米FDX低功耗半导体节点上成功流片,裸片尺寸为26.97平方毫米。测试封装是FCBGA类型,有22 x 22个焊球的网格阵列,该芯片的目标频率为1GHz。在下面的图片中,你可以看到经典的"Hello World "测试正在新平台上进行。

该芯片的近期前景是不断改进,与其他仍需设计的 HPC IP 一起,一旦一切准备就绪,EPI 计划将其整合到一个强大的 HPC 系统中,用于各种工作负载。

EETOP 官方微信

创芯大讲堂 在线教育

创芯老字号 半导体快讯

相关文章

0

0