Cortex-X1是5月26日与Cortex-A78一起公布的CXC(Cortex-X定制)计划的第一款产品,之前曾经做过简单的介绍。在这次线上研讨会上Arm公司对 Cortex-X1做了更加详细的介绍。(图一)。

·

X1面向更高的性能而不是效率,是一个不同于传统产品的高性能产品线。

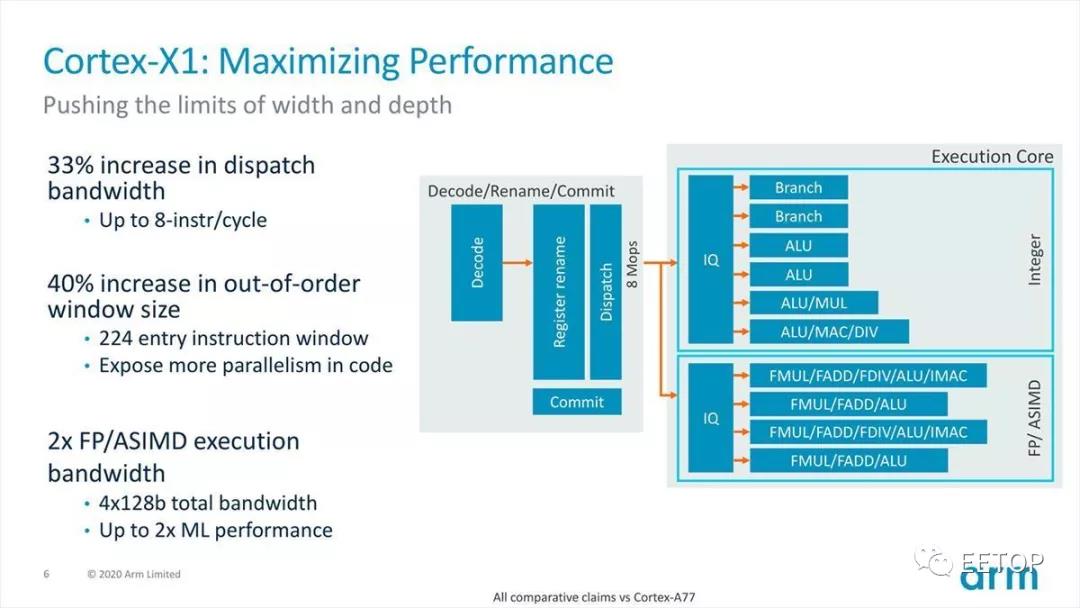

在前端方面,BTB的容量提高了50%,X1 Fetch的指令5条/周期,Micro-Op的Cache有8个微操作/周期的指令要传递给解码器。而Cortex-A78 Fetch的指令为4条/周期,Micro-Op Cache为6个微操作/周期。BranchPredictor最多可以处理2个Branch/cycle,这对于Cortex-X1和Cortex-A78来说是一样的。

指令分派同时发出8条微码(图3)。ALU有6个执行单元,FPU有4个执行单元。此外,据说由于指令分派的增强,乱序窗口的大小增加了40%。尽管未在此处列出,但ROB等似乎也在变大。此外,FP / ASIMD端的IQ大小将增加一倍。

就LSU而言,Cortex-X1(图4)和Cortex-A78(图5)的结构本身完全相同。数据L1和L2的带宽增加了一倍的是与Cortex-A77相比,并且认为由加载/存储单元本身处理的数据量已从16字节/周期增加到32字节/周期。此外,可以看出正在采取适合数据访问的措施,例如将动态加载窗口大小增加33%,将L2TLB增加66%。此外,L2已增强到最大1MB,并且还支持8MB L3。

图4:双FPU的加载/存储单元有点差。一个周期最多可以输出512位数据

·

图5:这是Cortex-A78,L1-D本身是一个选项,并且不支持L3,这可能是因为性能/面积比或性能/功耗比。

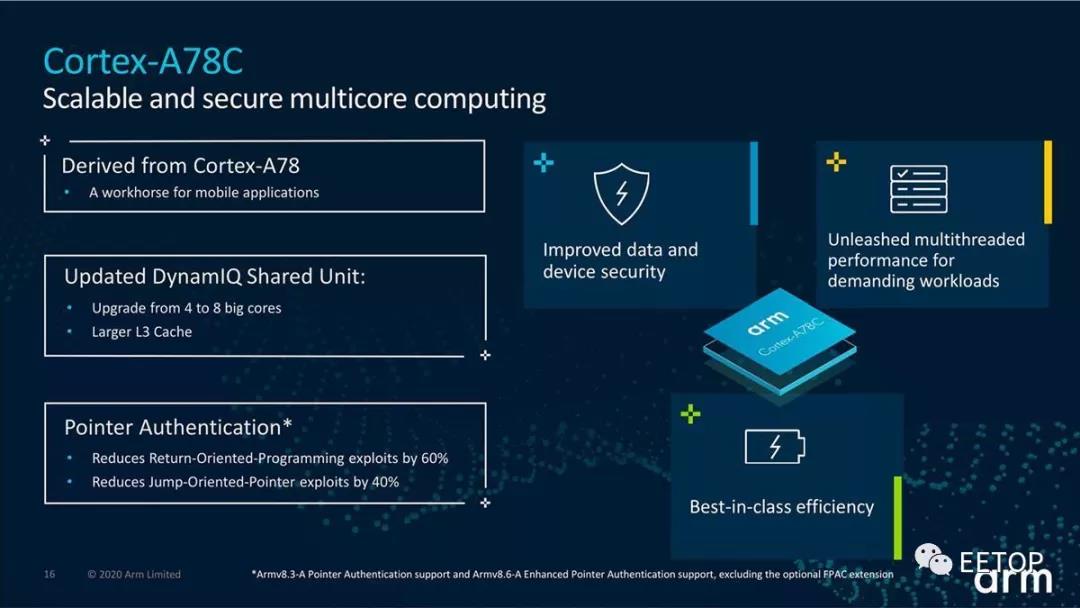

Cortex-A78C适用于移动设备,也适用于边缘应用

接下来是Cortex-A78C。这是Cortex-A78的衍生产品,尽管它是供移动使用的,但我们认为它更适合于固定设备或IoT Edge(图6)。

图6:与Cortex-A78的唯一区别是多核配置和安全性。

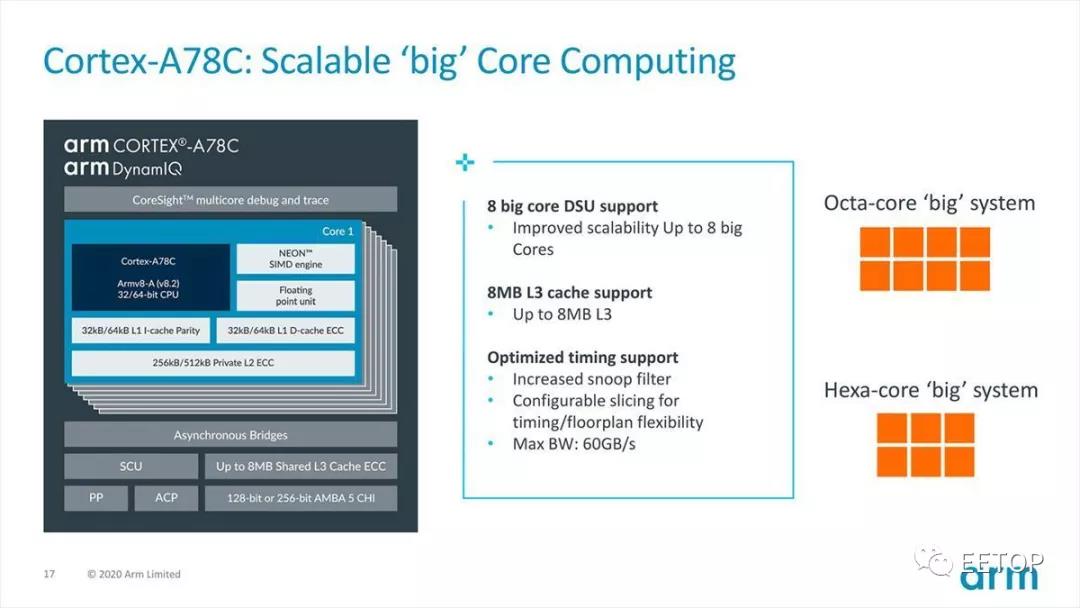

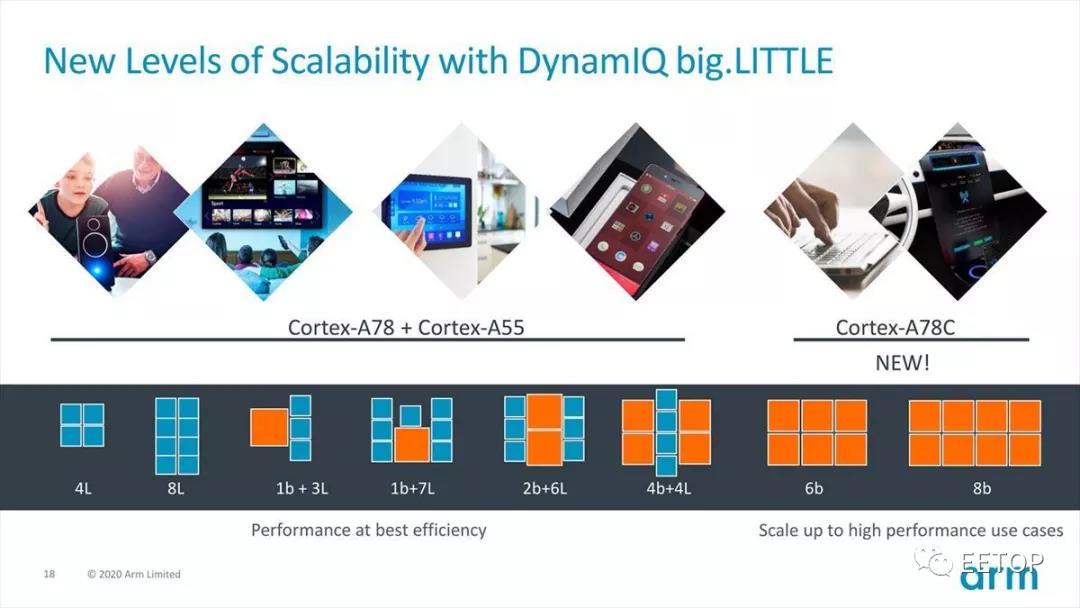

首先是多核配置。在使用DynamIQ的所谓big.LITTLE配置中,Cortex-A78成为大内核,Cortex-A55合并为LITTLE内核,但Cortex-A78C是统一的,也就是说,所有内核都是Cortex-A78C,允许6到8个核心和高达8MB的L3(图7)。

图7:使用了DynamIQ,但是没有核心调度(因此它不是big.LITTLE)

这款Corte-A78C的目标被定义为“大屏幕设备”,但是当您查看图8时,您还会看到笔记本PC和几乎像PC的车载设备。

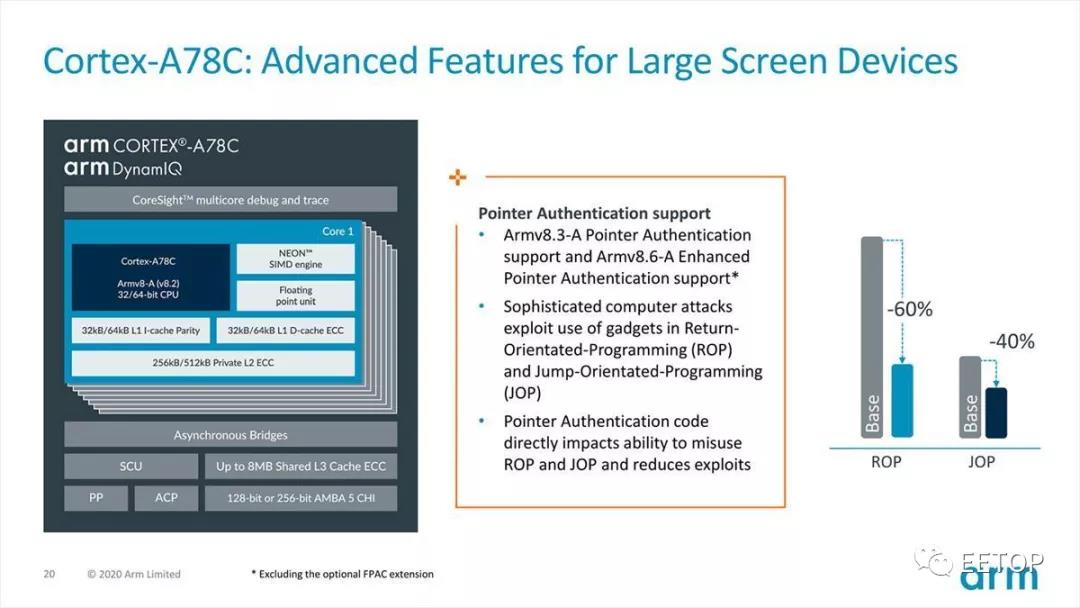

在Cortex-A78C中还增加了更多的安全性设计。ROP(面向返回的程序)或JOB(面向跳转的程序设计)是一种经常用于未经授权的程序入侵的技术,在预先将恶意代码加载到内存中后,其跳转类似于Return或Jump。它是一种重写目标并将控制权转移到恶意代码的方法。为此,Arm v8.3-a添加了一个称为指针身份验证代码(PAC)的功能。这是一种用系统中注册的PAC替换部分跳转目标地址的机制,如果重写了跳转目标地址,则PAC将消失,因此将其判断为无效的跳转目标,并且将中断执行。在那儿。它本身也已安装在Cortex-A78中,但是Cortex-A78C将能够使用Arm v8.6-A(由Matterhorn实现)提供的增强指针认证代码(EPAC)。(图9)。

目前,Arm尚未正式发布Cortex-A78C。

原文链接:https://news.mynavi.jp/article/20201102-1449269/

EETOP 官方微信

创芯大讲堂 在线教育

创芯老字号 半导体快讯

相关文章

0

0