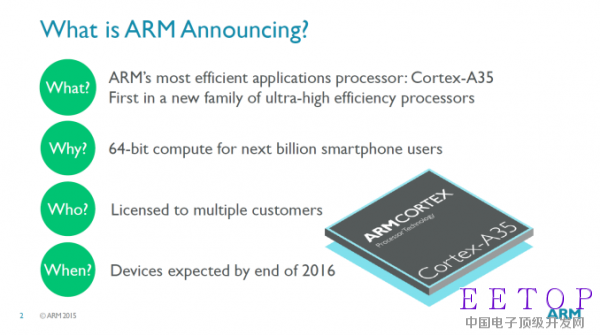

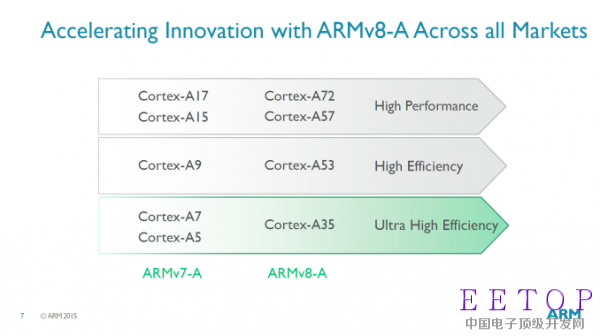

ARM今天宣布了一颗全新设计的CPU Cortex-A35,定位于低功耗的低端手机、可穿戴、物联网等领域。从这张图上就可以清晰地看到A35的位置:它也是基于ARMv8-A 64位架构的,但被放置在Cortex-A53的下边,取代对象则是32位的Cortex-A7/A5两个老核心。

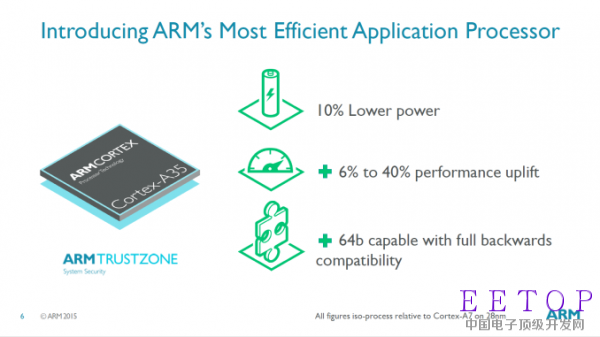

ARM宣称,A35是其有史以来能效最高的处理器,目标功耗不超过125毫瓦,而且已经在28nm工艺、1GHz频率下做到了90毫瓦,因此采用16/14nm工艺的话,可以在保持功耗不变甚至更低的前提下,轻松超过2GHz。

它还可以和A53、A57、A72等大核心搭配,组成big.LITTLE混合架构系统,进一步提升系统能效。

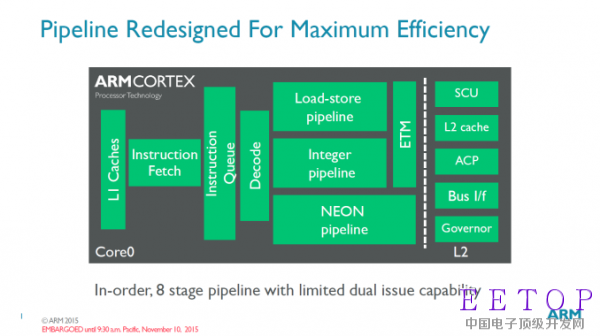

A35在架构上和A53、A7类似还是顺序有限双发射设计,8级流水线,但是精心优化改进了每一个模块,甚至融入了A72上的而一些最新元素,性能和能效都大幅度提升。

尤其是在前端,A35重新设计了指令预取单元,提升了分支预测精度,指令预取带宽更加平衡,指令队列也更小了。

它还采用了A53的缓存、内存架构,可配置8-64KB一级指令和数据缓存、128KB-1MB二级缓存,加入了NEON/FP单元,改进了存储性能,支持完整流水线的双精度乘法,还为CPU核心、NEON流水线都配备了硬件保留状态(独立电源域)以提升电源管理效率。

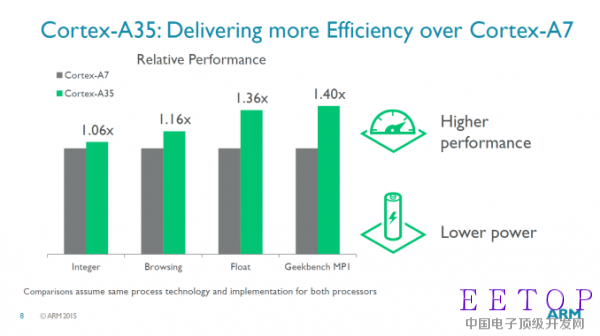

ARM宣称,在同样的工艺、频率下,A35的功耗可比A7低大约10%,同时性能提升6-40%,尤其是在浮点工作中。

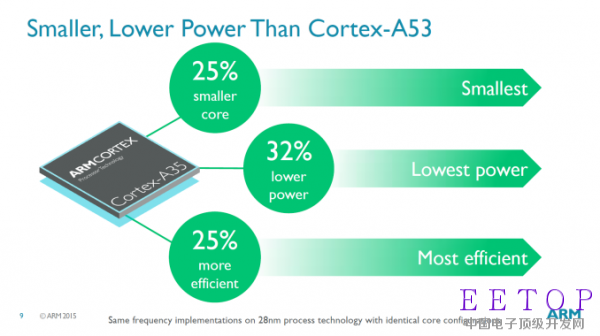

而对比A53,它可以保留80-100%的性能,但是功耗降低32%、面积缩小25%,能效提升25%。

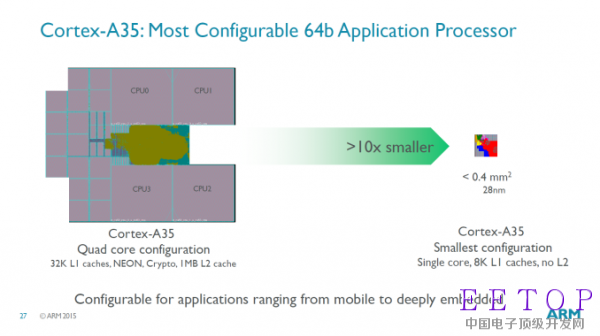

在28nm工艺、四核心、32KB一级缓存、1MB二级缓存、NEON和加密单元的高配置下,A35处理器的面积大约是4平方毫米,而如果做成单核心、8KB一级缓存、无二级缓存和NEON/加密单元,则能小于0.4平方毫米。

A35核心已经有多家厂商签署授权,首批设备预计2016年底面世。