PCIe 6之后,敢问路在何方

2023-11-21 13:44:46 泰克PCIe Express® 物理层先从 Gen 4.0 飞速发展到了 Gen 5.0,最后升级至 Gen 6.0,且 6.0 规范包含了开发硅芯片所需的一切。数据传输速率从 16 Gt/s 提升到 32 GT/s,Gen 6.0 更是增加到了 64 GT/s(每秒千兆传输速率)。而且,首次采用了PAM4多级信号调制技术,允许我们在单个单位时间内编码两位信息。借此,我们将 Gen 5.0 的数据传输速率增加了一倍。

在今年的泰克创新论坛上,我有幸参加了一场小组讨论,与我一同参与的还有两位业内专家:新思科技 (Synopsys) 的 Madhumita Sanyal 和安立公司 (Anritsu) 的 Hiroshi Goto。我们讨论了最新 PCIe 版本面临的挑战以及 PCIe 7.0 可能面临的挑战。PCIe Express 6.0的开发和设计仍在不断演化和成熟中,包括外形标准、测试规范等等。然而,PCI-SIG®已经宣布并已经开始了Gen 7.0的开发,我们预计到2025年将会有一个基本规范。我们有望实现每秒128千兆传输速率和与Gen 6.0一样的PAM4信号调制技术。

正如Madhumita所言:

“现在正处于一个非常有趣的时代,传输速率从 64 Gt/s 提升到了 128 GT/s。这相当于要求具有以下特性的以太网连接:1.6 TB 带宽,16 个传输速率为 128 Gt/s 的通道,总传输速率为 2 TB/s 且是单向,这是以太网世界的要求。并且保留了 PAM4,奈奎斯特现在为 32 GB,但需要向后兼容所有之前版本。

“我认为它仍会使用 Flits,谁知道哪种 FEC(前向纠错码)更强大呢?需要 FEC 就像以太网 LAN 需要 Reed Solomon 纠删码一样,也可能仍然使用轻型 FEC 就可以,也会提升数据传输速率。当然,协议本身可能会进行极大的改进。我认为电气设备将越来越可靠,具体取决于 PCI-SIG 如何定义通道。我们可能需要新的主板、连接器和电缆。SERDES 发送器和接收器架构肯定会面临一些新的挑战。”

Hiroshi Goto补充道:

“内容增加了,通道损耗有多少?从 Gen 5.0 到 Gen 6.0,从 32 GT/s 到 64 GT/s——P 和 N 之间的时钟偏差无论是正还是负,现在都极其关键。一毫米的电缆差异会带来五皮秒的失配。所以,P 和 N 的时钟偏差失配也会产生重要影响。

“人们已经做了大量工作来研究如何保持与卡机电 (CEM) 连接器的向后兼容性。我认为这是需要密切关注的问题。我们是否能够继续实现向后兼容性?我们是否必须考虑从主机到端点的替代连接类型?”

小组讨论结束后,泰克参加了 2023 年 6 月 13 日至 2023 年 6 月 14 日在美国加州圣克拉拉举行的 PCI-SIG 开发者大会,会上 PCI-SIG 宣布了 PCI Express (PCIe) 7.0 规范已升级至 0.3 版。

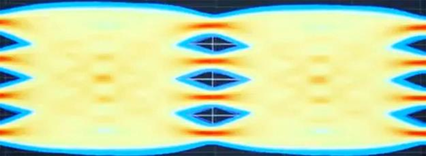

在该活动上,新思科技进行了一次所谓的“窥探式”演示,展示了PCIe 7.0即将达到的128 GT/s的数据传输速率。在演示中,新思科技评估板将 PRBS 模式发送到泰克 DPO70000SX 示波器上。所有三个 128 GT/s PAM4 眼图均打开,三者之间具有良好的线性度、低抖动和良好的比率电平失配 (RLM)。

成功的 128GT/s PAM4 眼图

在第二场演示中,安利公司重点展示了安利 MP1900A 误码检测器与泰克 DPO70000SX 实时示波器以及新思科技 PCIe 6.0 PHY & 控制器 IP 在端到端系统中的兼容表现,清晰显示了 FEC 应用前后的误码率对比情况。 在此演示中,泰克示波器校准的 33db 应力眼图由充当主机的安利误码检测器发送到具有 PHY 端控制器的新思科技端到端解决方案。接收器对受压的模式进行均衡,并将信号通过控制器回环至 PHY 发送器,再由发送器将信号返回至安利误码检测器。包括 Gen 6 阶段 1-3 在内的所有代际的链路训练均已完成且通过了测试。