摩尔定律死不死?

2019-12-05 12:51:51 金捷幡2018年是英特尔悲哀的一年。就在公司50周年大庆前一个月,挤了五年牙膏的CEO柯再奇因桃色事件辞职。

外界猜测,这只是董事会找的一个小借口干掉他,因为本身这个恋情微不足道。

最关键的是,柯再奇简直就是摩尔定律的反义词。在他任内,从14nm到14nm+++尴尬无比。而摩尔定律就是英特尔的基本法。

2018年,在半导体制程技术上曾遥遥领先半个世纪的英特尔被台积电反超。老陪衬AMD的RyZen居然在也迎头赶上。

Nvidia的黄仁勋说,摩尔定律已经死啦。一代巨擎Risc先驱David Patterson也说摩尔定律死了。

这几乎等于说,英特尔存在的意义消失了。一个科技界的指路明灯变成了一个普通的赚钱机器。

一

如果单看英特尔的财报,总体来说还是不错的。虽然在新产品上捉襟见肘,但是搭着云计算强劲的东风,英特尔的CPU还是供不应求。

如果时光倒流到十多年前,英特尔一定后悔两次拒绝苹果的日子。因为苹果培养了它的两大对手:三星和台积电。

在iPhone第一代发布前一年,英特尔拒绝了为乔布斯提供手机CPU并卖掉了自己的ARM分部XScale。苹果选择了三星。

2012-2013年,苹果为了去三星化寻求iPhone 5s的A7处理器代工厂。传闻中的候选人英特尔却没有接,台积电当时也没准备好接这么大的单子。

又在三星忍了一年的苹果,砸巨资投向台积电,终于实现了20nm A8的量产。当年英特尔已经开始量产14nm,领先台积电1-1.5代。苹果对CPU性能的图腾式要求倒逼了台积电的一路狂奔。

半导体先进制程需要太多资金的投入,苹果这个大客户的驱动终于给台积电井喷的动力,并在7nm站到巅峰。而格芯很明显是先进制程客户太少,导致没有钱继续军备竞赛。

二

事后诸葛亮是没有意义的,错误谁都犯过:乔布斯当年也清仓过ARM的股票,微软也清仓过苹果的股票。

我们八卦了半天,还是要回到摩尔定律这个话题。

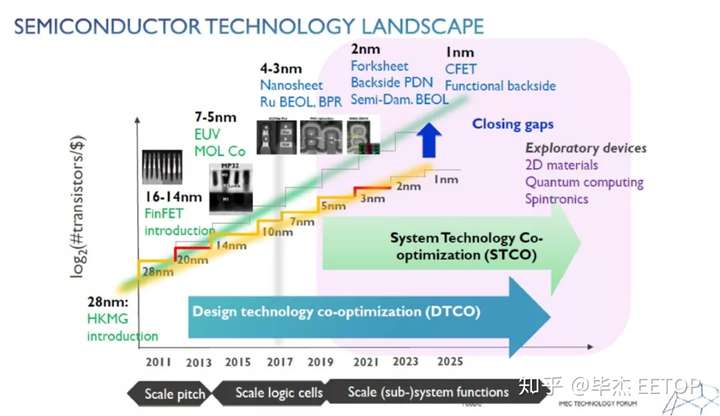

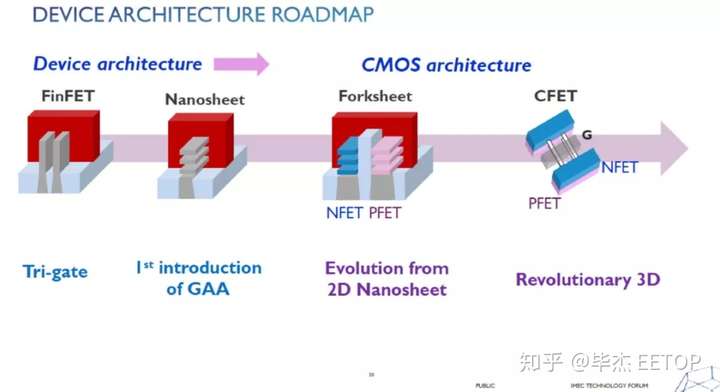

在英特尔灯塔暗淡的同时,大洋彼岸的比利时小镇鲁汶则熠熠生辉。下图是IMEC最新路线图,1nm已经正式出场。其实IMEC数年前就对此坚信不疑,而英特尔的Roadmap早就沦为平庸。

(Photo Credit: IMEC)

IMEC是尖端技术回归欧洲的一个象征。作为ASML的铁杆盟友并部署了最新NXE3400系列EUV的半导体研究重镇,IMEC也是High NA EUV的原型机联合研发合作伙伴。因此IMEC是最有底气说,它在真机上实现了1~3nm技术。

下图是ASML的路线图。由于High NA EUV已经设计完成,所以从光刻角度认为至少未来十年摩尔定律还在掌握之中。

(Photo Credit: ASML)

下图是High NA超净室里的巨型光学测量真空仓和巨大的EUV反射镜机械手。

(Photo Credit: ASML)

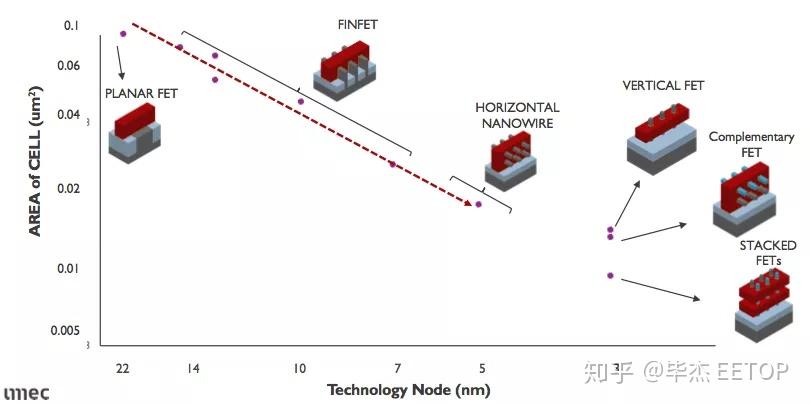

IMEC认为,超越5nm以后,晶体管Cell的模式可能是各种形状的FET管子。

(Photo Credit: IMEC)

有没有越来越像乐高积木的感觉,接下来粗浅解释一下一些基础知识。

三

首先,有人会质疑道:原子直径才0.1nm(1 Å),怎么可能把这么复杂的晶体管做到1nm。

确实如此。目前所谓制程技术或技术节点多少nm,并不是晶体管做到这么小了。

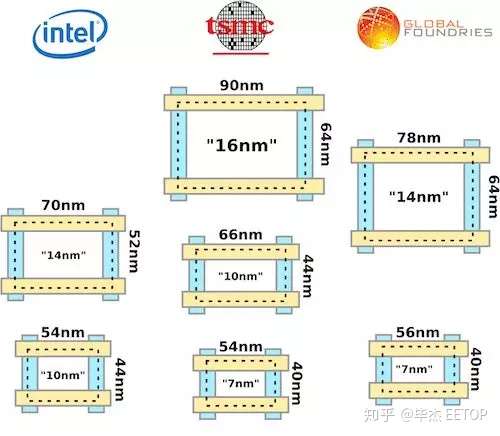

早期晶体管的缩小都是类似二维的,为了达到摩尔定律,长宽各缩小到0.7倍则面积缩小近一半(0.7x0.7=0.5)。传统ITRS定义技术节点是最小金属间距(MMP,即下图蓝色那根)的一半。但到了20/22nm引入FinFET以后,MMP的减少开始变得很慢,但是因为3D化后晶体管数量仍旧激增,厂商再用1/2MMP就显示不出来技术进步了。因此各家的命名就开始乱了起来:

20nm x0.7=14nm,所以新一代叫14nm

14nm x0.7=9.8nm, 所以再新一代叫10nm

10nm x0.7=7nm, 所以下一代叫7nm

7nm x0.7=4.9nm, 所以再下一代叫5nm

(请注意,上面这些0.7并未真正物理出现,只是假想如果二维缩小0.7而已。实际上看下图台积电10nm到7nm,MMP距离只是从42/44nm降到40nm)

(Photo Credit: WikiChip)

从上图看,英特尔的10nm和台积电的7nm平面基础尺寸是近似的。为了对比技术差距,单位面积的晶体管数成为一个好方法。据分析数据,两者每平方毫米都是一亿个晶体管左右。但台积电早已量产(麒麟980/990,A12/A13,AMD Ryzen 3000等),但英特尔多年还是搞不定良率问题。

四

有专家猜测,英特尔10nm碰到的问题可能和它家激进地把导体从铜全面转到钴有关,而台积电和三星仍然用铜或镀钴。铜是很好的导体,但有个很讨厌的特性,就是在纳米尺度电阻会激增。

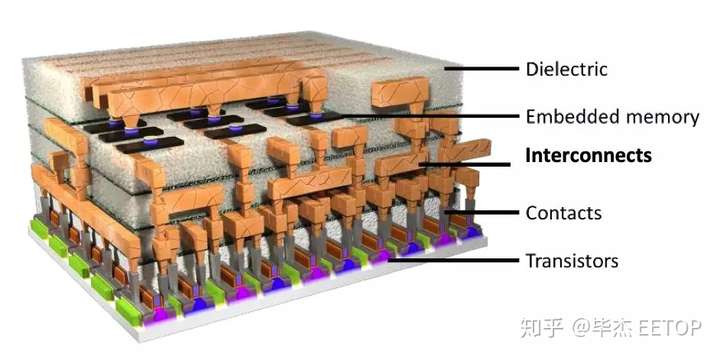

下图是很漂亮的示意图,图中铜颜色那个就是铜。实际的芯片里这些金属层可以有12层之多,把最底下的晶体管互联起来形成电路。

这就是最微观层面搭建的宏伟大厦。想想看,这是在芝麻大的空间里,上亿个晶体管上面复杂搭建了上亿根铜筋的混凝土建筑。

金属钌是替代铜的另一个选择。而在晶体管材料上,硅锗合金和拥有更佳电性能的铟、镓和砷化物也在被深度考虑或已应用。

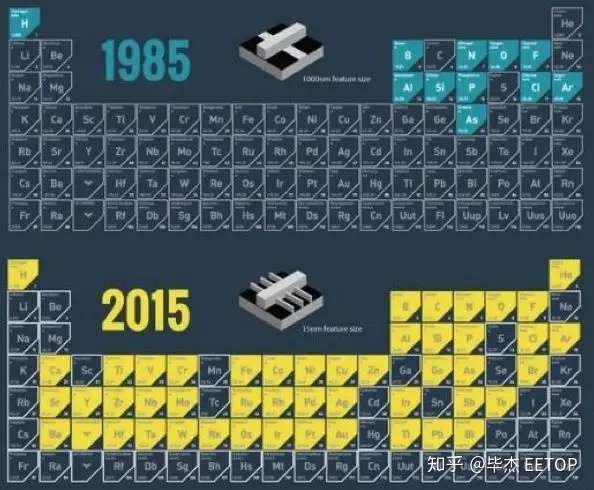

下图很好地展示了在半导体发展历程中,人类绞尽脑汁使用了元素周期表上的各种可能。这还不包括各种化合物。

(Photo Credit: SEMI)

看到这种精神,你认为让科技精英们直接放弃摩尔定律,会那么容易吗?

五

5nm制程基本上还是会用已经成熟的FinFET架构,FinFET比平面Planar更大的电流和更快的开关速度足够支撑到5nm。只是光刻必须要用到EUV,否则掩模的层数要多到失控了。

(Photo Credit: IMEC)

目前各家的3nm方案都是更加立体的FET,nanosheet和nanowire等统称为GAA(Gate all around)。“到处都是闸门”,这个名字显示了这些小乐高晶体管的诡异模样。它们还包括了碳纳米管等各种复杂的材料。

IMEC目前笃信CFET将是打开1nm大门的钥匙,到那时各厂市场部宣传的单位将是埃米而不是纳米。

虽然这些技术都在实验室实现了,但是距离量产还有数不清的险阻。但最大的障碍是:钱。

目前开发一款7nm芯片的成本是3亿美元,5nm预测是5亿美元,而3nm很可能到10亿美元。

究竟未来能有几家公司需要做这种芯片呢?

这时,可怕的摩尔第二定律也闪现了威力:“新晶圆厂的成本每两年翻一番”。

目前新7nm工厂是150亿美元,那么5nm工厂将需要投资300亿美元,3nm则理论上是600亿美元。

六

正是因为各种不确定性或各种悲观,否定摩尔定律的声音越来越多。确实,对于目前硅架构存在量子隧穿效应极限。

不过,可行的方法不仅只有继续缩小晶体管的尺寸,还包括做多层晶体管的方案和叠加晶圆的方案等。

英特尔也在试图改进处理器架构的方法来实现另类摩尔定律,因为我们的最终目的是为了实现单位芯片面积计算力的每年提高。早期CPU性能是靠提高主频实现的,但后来英特尔的Core架构和AMD的Zen架构都成功实现了主频不变算力的突破,所以这个思路一定还有突破空间。

从目前情况看,至少未来十年人类还有充足的技术手段继续倍增芯片性能。再往后,也许量子计算真的会到来?

关键词: 摩尔定律