重磅!英特尔推出全新FPGA 架构:AgileX | 10nm工艺,支持PCIE 5.0、UPI,更方便实现与Xeon互连

2019-04-03 08:44:27 EETOP 原创

自从英特尔几年前以167亿美元的价格收购Altera以来,FPGA产品组合的推出基本上是英特尔时代之前的产物。然而,今天情况发生了变化,英特尔宣布了其首款完全由英特尔独立设计的FPGA,基于其内部10nm工艺,使用全新Agilex命名。这一系列新产品将于今年晚些时候推出样片,并在一个单一的平台上提供模拟、数字、内存、定制IO和eASIC变体的混合。

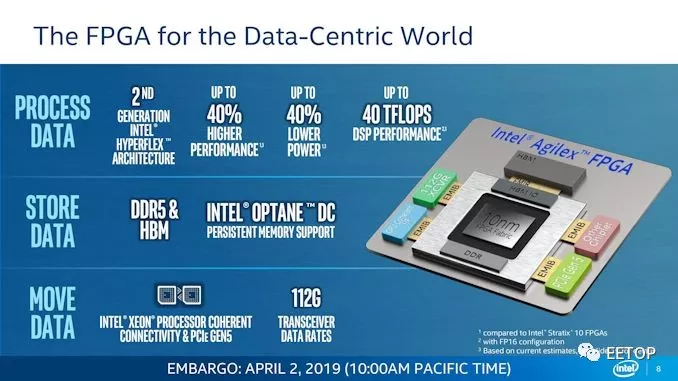

从本质上讲,AgileX是一个异构的逻辑,可以将FPGA内核(包括可配置的DSP和可选的Arm SoC)与Xeon处理器,定制芯片和I/O设备连接起来。FPGA和其他组件之间的连接是通过英特尔的嵌入式多芯片互连桥接器(EMIB)实现的,该技术旨在将单个封装内的不同芯片连接在一起。

FPGA部件将在英特尔的10纳米工艺节点上制造,毫无疑问,与目前的Stratix 10 FPGA相比,英特尔无疑将提供高出40%的性能和40%的低功耗。目前尚不清楚这种更好的性能和效率有多少归功于强化的DSP。

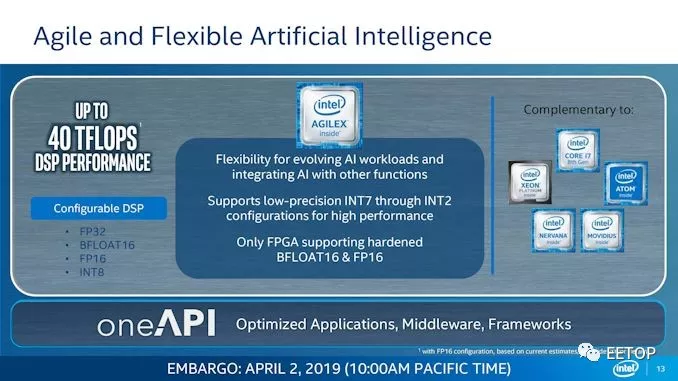

根据英特尔的说法,AgileX DSP在16位时提供多达40 TFLOP,并支持FP32,bfloat16,FP16和INT8数字格式。它还可以配置为支持较低精度的整数 - INT7到INT2之间的任何值。英特尔表示,这是第一款支持硬件实现bfloat16和FP16的FPGA。鉴于这些格式,看起来AgileX将非常适合用于推理经过训练神经网络。

Agilex FPGA建立在与Stratix相似的设计原则之上 - Stratix是一个集中的FPGA,具有强化功能和基于客户要求的多种不同技术的外部连接。对于这些外部连接,英特尔正在使用其嵌入式多芯片互连桥接(EMIB)技术,在给出的示例中,该技术可以扩展到其他芯片组。英特尔的一些小芯片建议包括高带宽内存(HBM),下一代112G收发器,PCIe Gen 5.0,Compute eXpress Link接口(通过PCIe 5.0),额外的CPU高速缓存一致性互连以及其他小芯片/ IP由客户。除此之外,Agilex还将支持英特尔的Optane DC持久内存。

自收购Altera以来,英特尔就致力实现FGPA与Xeon的互联。英特尔在去年已经发布过一款用最初的Xeon-FGPA混合产品,但一直没有出现任何成熟商业应用。

最新的AgileX FPGA已可以实现与Xeon处理器连接,通过缓存一致的UltraPath Interconnect(UPI)方式实现连接,允许FGPA和Xeon存储器共享相同的地址空间(UPI是2017年夏天在Skylake Xeon SP处理器中引入的QPI的更高效和更快(10.4 GT / sec)的替代品)。它在Agilex中的存在体现了英特尔的FPGA可以充当CPU的真正对等体,而不仅仅是挂在PCI-Express总线上的协处理器。

对于更专业的处理,AgileX设备还可以连接来自英特尔和第三方提供商的定制芯片。英特尔提出的一项关键技术是eASIC,它是从2018年购买的同名公司获得的。

它可以将可配置的逻辑块转换为FPGA和ASIC之间的中间件。根据英特尔的说法,eASIC“提供更接近标准单元ASIC的性能和功效,但设计时间更短,而且与ASIC相关的非经常性工程成本的一小部分。”声称它可以提供在短短五周内测试原型。鉴于此,我们感觉eASIC技术将在不久的将来在其他英特尔产品中亮相。

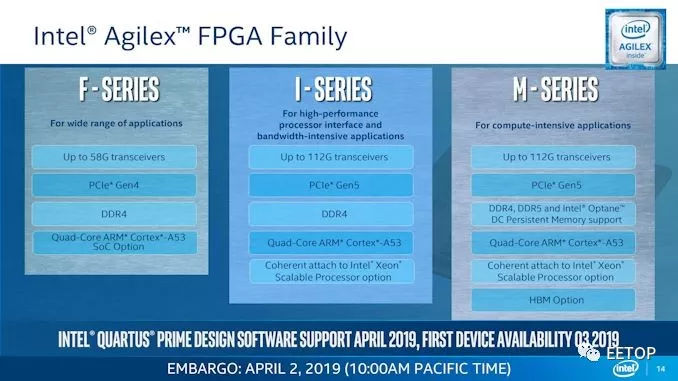

异构性也扩展到AgileX内存和I/O. 该平台支持DDR4,DDR5和高带宽内存(HBM),以及英特尔自己的Optane DC持久性内存,而设备连接则由PCI-Express 4.0或5.0提供。还提供112G SerDes收发器接口,其中四个通道足以提供400Gb/秒的网络链路。

AgileX产品系列分为F系列,I系列和M系列。下图显示了每个系列中可用的各种界面和选项,随着您提升字母表,功能也会增加。

AgileX可以用在多种领域,从超大规模云和企业数据中心到边缘计算、嵌入式应用等。。人工智能也是很重要的应用,因为英特尔宣称其Agilex产品组合将对bfloat16和其他低精度数字格式提供强化支持,这些将通过英特尔的OneAPI战略进行管理。

EETOP 官方微信

创芯大讲堂 在线教育

创芯老字号 半导体快讯

相关文章

0

0